Experts dream that one day much of the Internet of Things (IoT) will power itself. But the trickle of energy most prototype systems can gather from the environment through ambient heat, light, radio waves, or even the metabolism of bacteria don’t easily give you enough voltage to power today’s transistors.

One solution: ditch the transistors in favor of micrometer-scale mechanical switches. According to research presented this week at the IEEE International Electron Device Meeting, nanoelectromechanical (NEM) relays can switch using just 50 millivolts, that’s about 1/15th of what’s used on today’s processors.

An inherent property of CMOS transistors called the subthreshold slope sets a lower limit to how little voltage you can use to turn a transistor on, explains Alice Ye, a graduate student at University of California, Berkeley in the laboratory of IEEE Fellow Tsu-Jae King Liu. But as manufacturers push closer to this limit, it becomes harder to turn transistors completely off. That is, current leaks across them even when they’re supposed to be turned off, wasting power.

“Ideally, you want a device with close to no off-state leakage and zero subthreshold swing,” says Ye. And, ideally, that’s what a NEM relay can deliver.

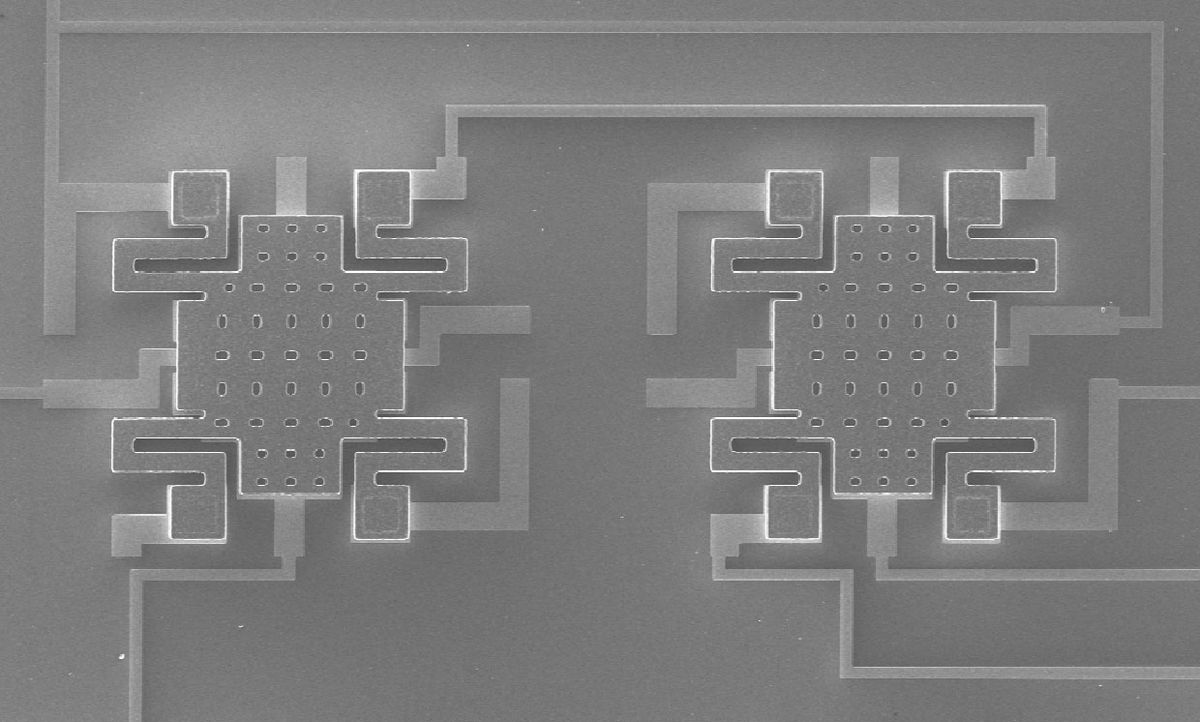

Ye presented research on relays that come closer to that ideal than ever before. The relays are basically thin, square platforms suspended by springs. Voltage applied to the platform—called the gate to mirror a transistor’s parts—pulls the platform down, contacting two sets of electrodes and allowing current to flow. Remove the voltage, and the gate springs back up, breaking the connection.

Liu’s lab has been researching NEMS relays for more than a decade, and the original versions were much less concerned with low-voltage operation. But in the past few years they have been working toward driving the supply voltage as low as it can go. That’s involved two innovations. The first was to “bias” the NEMS body. That is, they set a steady, unchanging voltage beneath the device. With this bias voltage set, it takes much less voltage on the gate to cause the relay to snap down onto the contacts.

The second innovation had to do with the contacts. Once the gate has slammed down on them, the metal-metal contact requires a bit of extra force to break. In practice this means that a relay that switches on at 200 millivolts, might not turn off until you reduce the voltage to 100 millivolts. To reduce this difference, called hysteresis voltage, Liu’s team first redesigned the switch to have two contacts instead of four. They also added a step to the manufacturing process that coats the surfaces in a single-molecule thick layer of lubricant. “It’s similar to Teflon so it has very low adhesion,” says Ye.

Combined, these reduced hysteresis voltage to an acceptable level, but at a cost. Instead of sharply switching on an off, the device now has a slight subthreshold swing, because the contacts have to squish the lubricant layer. Even so, the resulting devices could operate at 50 millivolts and be combined to form several types of logic gates.

Relays lend themselves to a different form of logic than CMOS transistors. Called pass-gate logic, it requires fewer devices to achieve the same output. Using earlier versions of the devices her group built multiple-gate systems including a 32-bit adder. “We know we can make these very complex,” says Liu.

Circuits made from NEMS relays have other advantages besides extremely low-voltage requirements, says Liu. For one, their switching characteristics should be stable over a wider range of temperatures than silicon systems. They also are inherently tolerant of radiation.

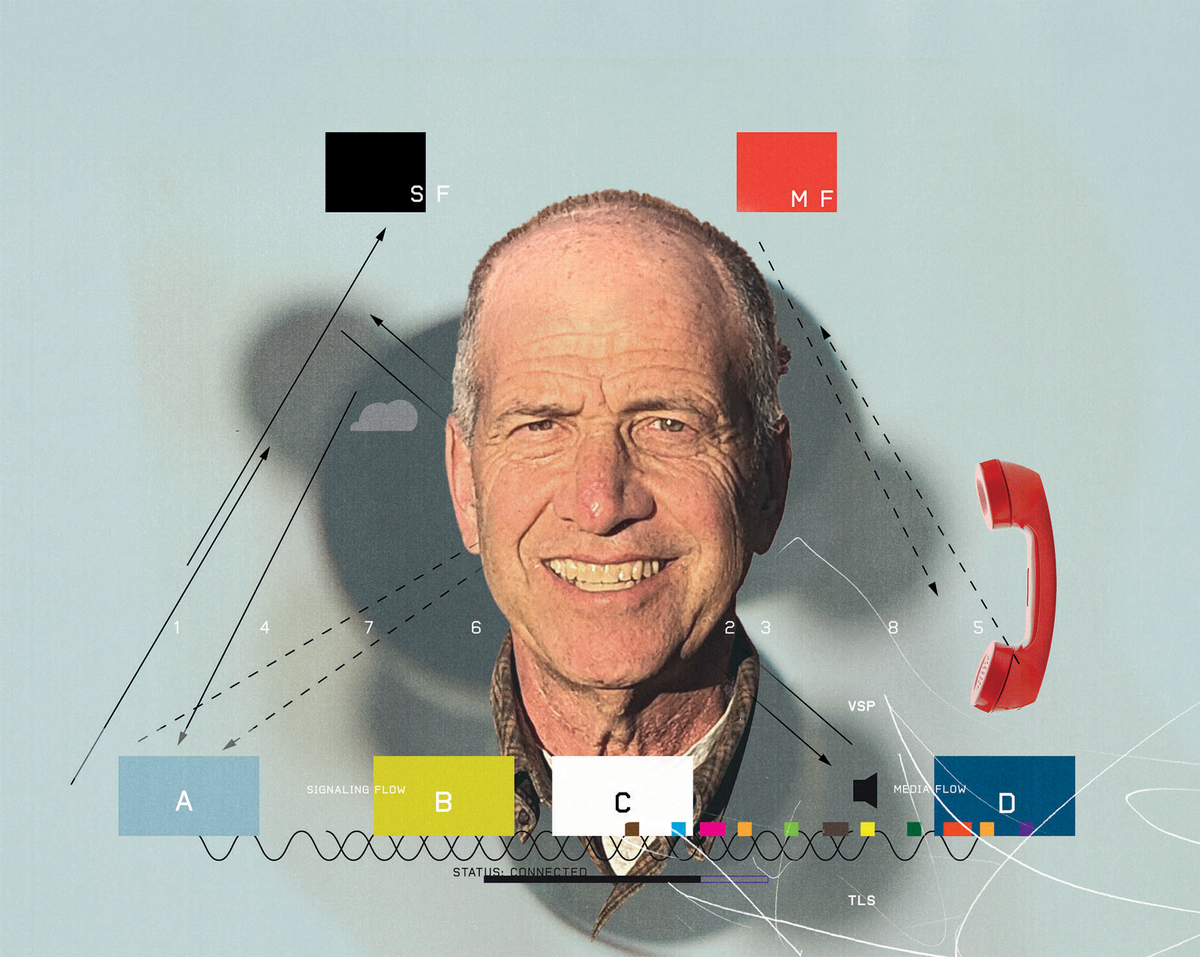

Liu’s team’s immediate next steps are to further reduce the relay’s operating voltage down to 10 mv. “I’m pretty optimistic” about this goal, says Liu. They are also working to integrate relays into standard CMOS chips. To do this, they’ve designed the relays so they can be built vertically to fit within the dozen or so levels of interconnect wiring that are stacked above the silicon in modern processors. Such hybrid systems could continually operate at a low level and then engage the main processor when triggered by the right event.

Samuel K. Moore is the senior editor at IEEE Spectrum in charge of semiconductors coverage. An IEEE member, he has a bachelor's degree in biomedical engineering from Brown University and a master's degree in journalism from New York University.