Today’s advanced chips use transistors whose most prominent feature is a vertical fin of silicon through which current flows when the device is switched on. But that design’s days may be numbered. IBM, for one, plans on moving to a design called “nanosheets” for the technology node due out in a few years. Qualcomm has other ideas.

In detailed simulations carried out with chip manufacturing tool maker Applied Materials and design automation giant Synopsys, Qualcomm engineers analyzed five design candidates for this next generation. In particular, they were looking for a difference between how individual transistors perform and how complete logic gates composed of them would perform.

The clear winner from this analysis wasn’t one of the established candidates but a new design Qualcomm engineers invented called a nanoring. They report their work in the December issue of IEEE Electron Device Letters.

“Device engineers or process engineers optimize for a very limited figure of merit,” says S.C. Song, a principal engineer at Qualcomm. For example, at the device level, much of the focus is on how well the transistor’s gate can control the flow of current through its channel. However, other aspects become more important when you look at complete logic gates instead of single transistors. In particular, Song and his team found that a device’s parasitic capacitance—energy lost during switching due to the presence of unintended capacitor structures—was the real issue.

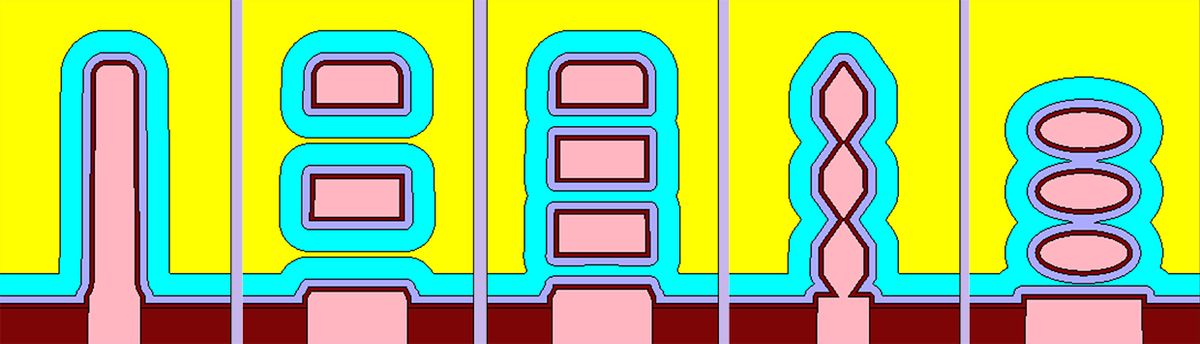

That’s what made the Qualcomm team choose their nanoring design over a variant of nanosheets, which they called nanoslabs. From the side, nanoslabs look like a stack of two or three rectangular slabs of silicon. Each slab is surrounded by a high-k dielectric and a metal gate electrode. Voltage at the gate produces an electric field in the silicon that allows current to flow through.

Completely surrounding each slab of silicon with the gate electrode gives good control over the flow of current, but it also introduces parasitic capacitance, because the structure between the slabs—silicon, insulator, metal, insulator, silicon—is basically a pair of capacitors.

Nanorings solve this by altering the shape of the silicon and incompletely filling the space between the slabs with metal. Baking the device in hydrogen causes the rectangular slabs to form into elongated ovals. This pinches the space between them so only the high-k dielectric completely surrounds them. The metal gate can’t quite make it all the way around, so there’s less capacitance. Yet, the gate’s electric field is still potent enough to throttle the flow of current.

“Capacitance scaling is the most challenging issue in cutting edge nodes below 7 nm,” says Chidi Chidambaram, vice president of the process technology team at Qualcomm. “Capacitance reduction from the non-current-contributing portion of structure...therefore is of utmost importance going forward.”

Despite the clear win in this simulation, the issue of which transistor Qualcomm will want in future chips is far from settled. Song and his collaborators plan to build and test devices and circuits with nanorings. And they also plan to simulate much more complex circuits and systems with nanorings, all the way up to a complete phone.

This final test is, in some ways, the one consumers will care most about. It will figure out how much more battery is left over in a smartphone after a regular day of use if that smartphone runs on nanorings.

Samuel K. Moore is the senior editor at IEEE Spectrum in charge of semiconductors coverage. An IEEE member, he has a bachelor's degree in biomedical engineering from Brown University and a master's degree in journalism from New York University.