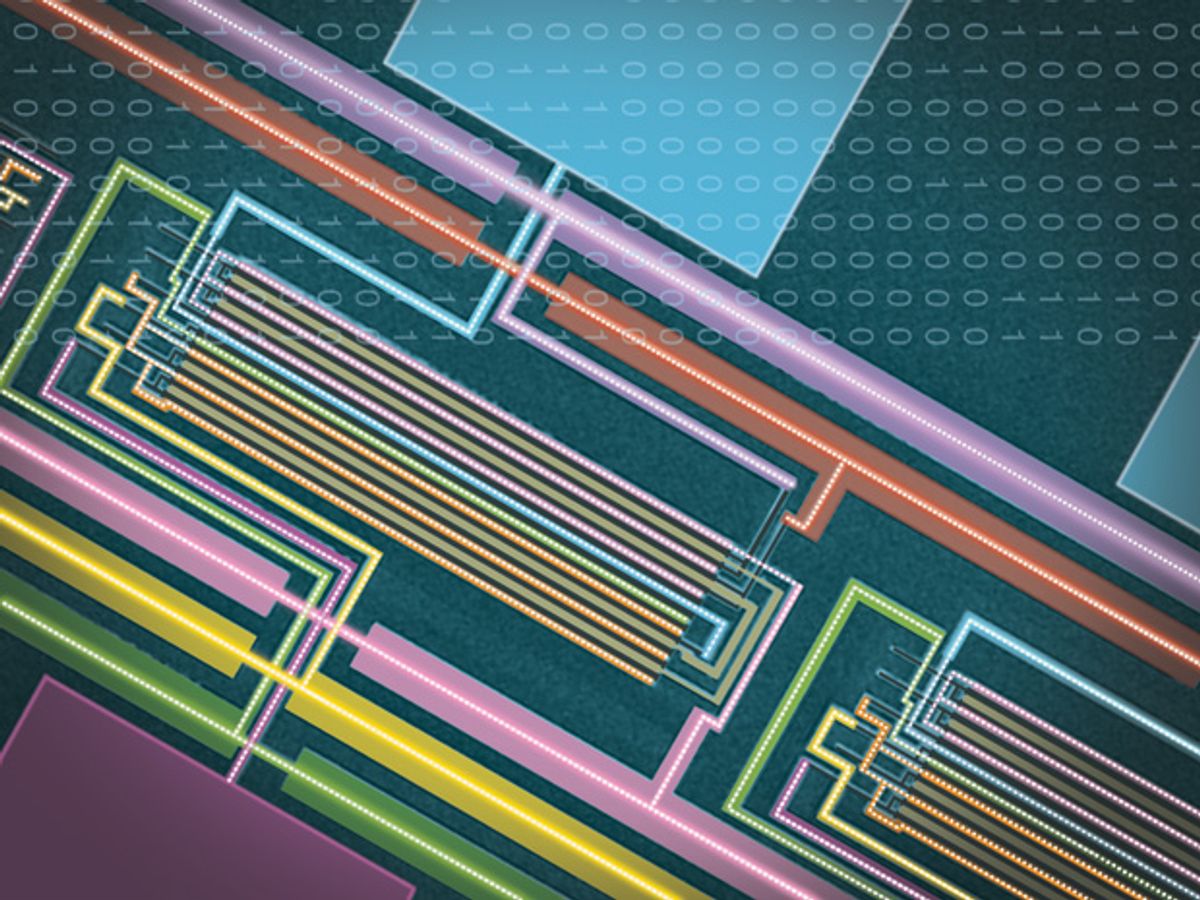

The days of silicon’s reign may be numbered. A team has built a computer using carbon nanotubes.

The computer is rudimentary by modern standards: it contains just 178 carbon-nanotube-based transistors to the billions of silicon-based switches in modern chips. It operates on only 1 bit of information, where today we rely on 32- and 64-bit machines. And it clocks in at just 1 kHz, about a million times slower than the application processors we find in modern smartphones.

Still, researchers say, the machine, developed at Stanford by a team led by professors H.-S. Philip Wong and Subhasish Mitra and described this week in Nature, is the first of its kind and an important step for a material that has long shown promise as an alternative to silicon.

"This is the first time that anybody has been able to put together a complete working computer based on any beyond-CMOS technology," says Naresh Shanbhag, a professor at the University of Illinois at Urbana-Champaign. (Shanbhag directs a chip research consortium called SONIC that includes Stanford University.)

Researchers are hunting for an alternative to silicon because the transistor is no longer shrinking like it used to. The switches leak current, and the circuits based on them get hot. The problem is only going to get worse as transistors get smaller and circuits get denser.

Carbon nanotubes, which are essentially rolled up, hollow sheets of carbon, have long shown promise as an alternative material. They are small, nanoscale structures that can theoretically be packed quite close together, and they exhibit very attractive electrical properties: current flows easily across them, and they can be switched on and off fairly easily.

The first carbon nanotube transistors emerged in 1998 out of research groups based at IBM and Delft University of Technology. Since then researchers have succeeded in building smaller circuits, but developing very large scale integration (VLSI) processes that could be used to mass produce chips based on the material has been slow going. “Everybody wanted to build a commercial or large-scale digital system using these materials, but they could not do it because of the substantial imperfections that are inherent in carbon nanotubes,” says Mitra.

There are two imperfections that have proved particularly problematic, say Mitra and his colleagues. One is that, although nanotubes can be grown fairly easily using chemical vapor deposition, the process tends to produce nanotubes with a mix of electrical properties: semiconducting and metallic. Metallic nanotubes are undesirable as they act as wires and can short out circuits.

The other stumbling block is one of alignment. Carbon nanotubes can be grown on a pre-patterned wafer so they form parallel tubes. But a small fraction inevitably are misaligned, and can cut across and connect with neighbors.

To make a process that could work in a commercial chip fab, the Stanford team developed a set of techniques they dub imperfection-immune design. They first eliminated the metallic nanotubes on their wafer by turning off all of the semiconducting nanotubes and driving a high current through the circuits. This caused the metallic nanotubes to overheat, oxidize, and ultimately vaporize into small puffs of carbon dioxide. The team then etched away sections of the mat of remaining nanotubes to form circuits. This etching was guided by an algorithm, based on graph theory, that can produce circuits that are mathematically guaranteed to work regardless of any imperfections, Mitra says, by cutting off at least part of any possible cross-cutting nanotube.

The computer, built by graduate student Max Shulakar, isn’t one we’d recognize today. It uses only p-type metal-oxide-semiconductor (PMOS) logic. PMOS transistors are switched on when a negative voltage is applied. NMOS switches work with positive voltage. Although PMOS logic was the first to emerge in computing, today’s logic chips use both to make complementary (CMOS) logic. The disadvantage of PMOS is that it is effectively always on: it is a sort of network or resistors that relies on the presence of transistors of variable widths to regulate the flow of current and create voltage drops.

But Shulaker and his colleagues show the computer is capable of everything you’d expect from a general purpose processor. It can run a basic operating system and multitask. It can perform counting and number sorting. They also demonstrate more modern silicon capabilities, by running 20 different instructions from the commercial MIPS instruction set.

How does the computer work? It uses just one instruction to perform all computations: SUBNEG (subtract and branch if negative). As Franz Kreupl, a professor of electrical engineering at the University of Munich in Germany, writes in an accompanying commentary:

SUBNEG takes the content of a first memory address, subtracts it from the content of a second memory address and stores the result in the second memory address. If the result of this subtraction is negative, it goes to a third memory address. Because the instruction contains this conditional statement, it guarantees Turing completeness -- that is, it can make any calculation if the computer has enough memory available.

Rudimentary as the computer is, Kreupl says it is a notable advance in the hunt for silicon alternatives. The new work could do a lot to draw more attention to carbon nanotubes, which have lost the spotlight in recent years to graphene. “A circuit as complex as this one has never been devised,” Kreupl says. “I think it’s an important step forward.”

There are of course, still a number of open questions. One is how well this approach will scale down. Working in an academic fab, the Stanford team was limited to an optical lithography resolution of just 1 micrometer, which limited the length of the carbon nanotubes transistors to about that distance (today silicon transistor dimensions are measured in the tens of nanometers). The density of the nanotubes patterned on the wafer was also low: just 5 per micrometer. That density would have to be boosted to 100 to 200 per micrometer, if not more, to increase speed and to make the process cost effective.

Much progress will depend on how uniformly the transistors can be laid down. "If the density varies too much, that would have an effect on the energy efficiency of the final circuit," Mitra says. There is work being done to address that issue. In the meantime, he says, we've reached a notable crossing point. "People said you couldn’t build anything big with carbon nanotubes," he says. "Now that question has been resolved."

Rachel Courtland, an unabashed astronomy aficionado, is a former senior associate editor at Spectrum. She now works in the editorial department at Nature. At Spectrum, she wrote about a variety of engineering efforts, including the quest for energy-producing fusion at the National Ignition Facility and the hunt for dark matter using an ultraquiet radio receiver. In 2014, she received a Neal Award for her feature on shrinking transistors and how the semiconductor industry talks about the challenge.