It was 1975, and Kurt Petersen was a smart young researcher, fresh out of the Ph.D. program in electrical engineering at MIT and working in the optics group at IBM's Almaden, Calif., research center. And he was bored. Roaming the massive complex one day, he came across a huge black stain on the linoleum tiles of an otherwise nondescript hallway. That stain would change his life and the course of an entire industry.

In search of the source of the stain—he was that bored—Petersen walked into the nearest lab. The stain, he found out, came from an ink spill. The lab was developing inkjet printer nozzles by etching precise holes in silicon.

Etching holes in silicon? It hadn't ever occurred to Petersen that you could etch holes in silicon. But then he remembered a poster he'd seen earlier that year, about an effort to create a miniature accelerometer on silicon. Suddenly the bigger picture snapped into focus: People were actually building tiny mechanical gadgets, their parts just a few micrometers across, out of silicon. Today we call those devices microelectromechanical systems, a.k.a. MEMS. And Petersen wanted to build MEMS, too.

He launched himself down a new career path, building MEMS technologies—including the devices that now screen every letter mailed in the United States for anthrax—and founding MEMS startups. For this contribution, and many more, Petersen will receive the 2019 IEEE Medal of Honor.

Soon after his encounter with the ink stain, Petersen began reading everything he could about making tiny mechanical devices out of silicon, in journals like IEEE Transactions on Electron Devices, Applied Physics Letters, and the Journal of the Electrochemical Society. Back then the category didn't even have a name, and there were only a couple of MEMS-type products on the market. He discovered that “there were dozens of people all over the world who had done different kinds of mechanical devices on silicon, but there was no community. The people doing the work didn't know about most of these other people."

Petersen then set out to build his first device. Looking at some of the inkjet nozzles under a microscope, he says, “I could see that when there was a defect, it left little freestanding, incredibly thin silicon dioxide beams hanging over. I thought, Wow, maybe these tiny mechanical structures can move around. Maybe they could deflect light, and I could build a light modulator." He used a process that's similar to one used in MEMS manufacturing today, patterning a layer of silicon dioxide on top of a sacrificial layer of epitaxial silicon, and then etching away the sacrificial layer. What's left is a silicon dioxide cantilever with a thin metal layer on top.

It took him three months to produce a few of the microscopic modulators, each about 100 micrometers long and 0.5 micrometers thick. He took them to the lab that housed IBM's scanning electron microscope, where a technician helped him install an electrical wire so he could apply a voltage to the devices and watch them move.

“She was fascinated," Petersen recalls. “She said she'd never seen anything move under the microscope."

Petersen spent the next five years creating as many different types of micromechanical devices out of silicon as he could, including accelerometers and electrical switches. He moved out of the optics group into a custom-designed laboratory that was just big enough to accommodate him and an intern.

Based on his deep dive into the literature and his own work, Petersen wrote an internal report on the emerging technology. “There were lots of mechanical structures that would potentially be of interest to IBM," he says, such as heads for optical and magnetic disk drives and more sophisticated inkjet nozzles. The company wasn't interested.

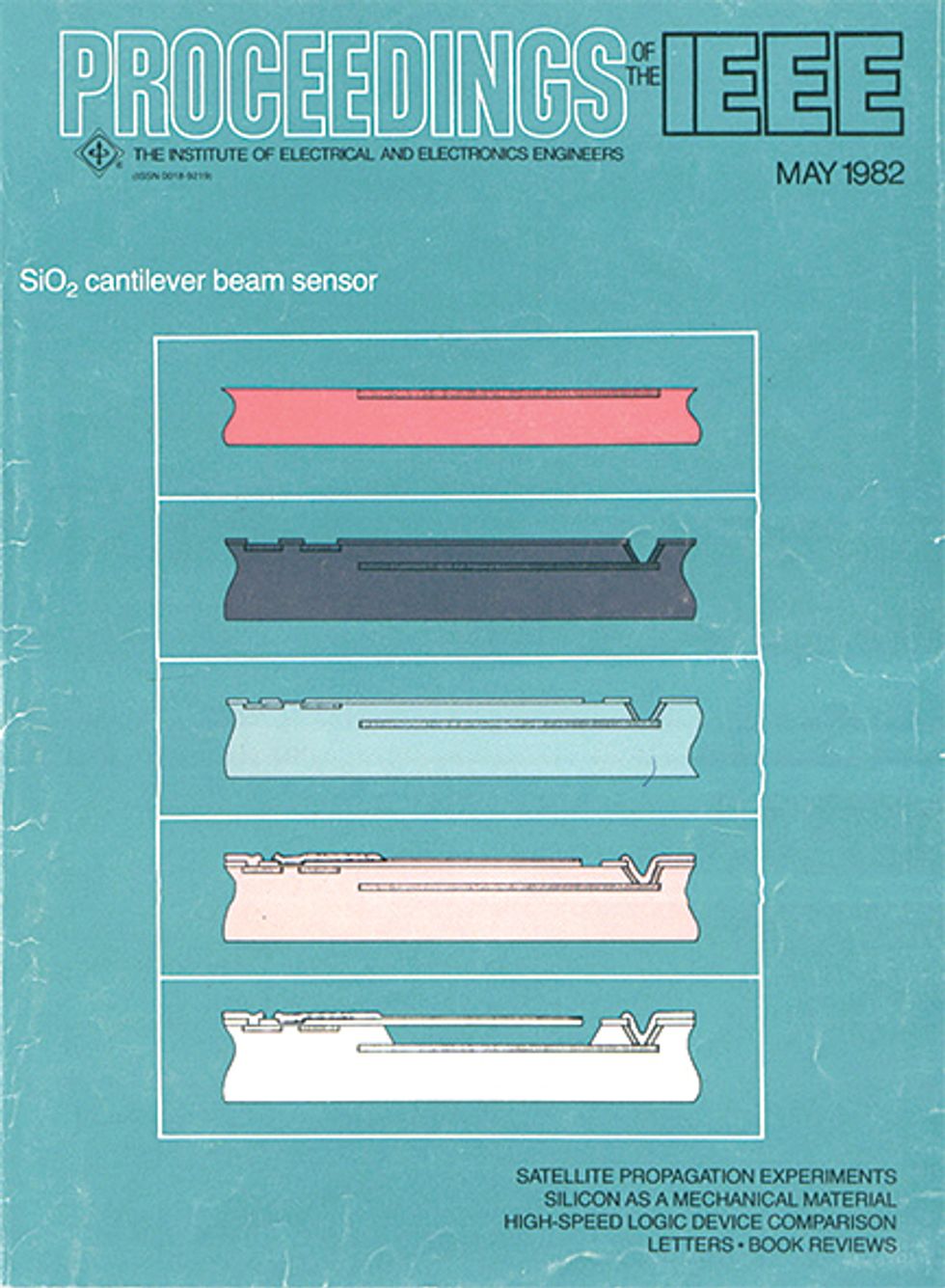

Petersen was disappointed, but he also realized that the devices weren't key to any of IBM's businesses. So he rewrote his report, removing IBM-proprietary information, and submitted it to the Proceedings of the IEEE—all 50 pages of it. The article, “Silicon as a Mechanical Material," became the cover story in May 1982 and helped establish MEMS as its own branch of technology.

The paper was comprehensive, looking at the mechanical properties of integrated circuit materials and various ways of etching those materials into shapes and structures. “It also speculated on things that came much later, like deep reactive-ion etching, which really revolutionized the field," he says. “Even today, people tell me reading that article is what got them interested in MEMS."

“We all read the paper when I was in grad school," says Greg Kovacs, now chief technology officer for SRI International, in Menlo Park, Calif. “He had a huge role in MEMS. What he did was more important, really, than founding the field—he inspired it. He is a superhero to me."

After the Proceedings paper came out, Petersen got invited to speak at conferences around the world, and researchers started showing up at Almaden to see him. “All sorts of people who were doing crazy things—like microfluidic cryogenic refrigerators—were somehow finding me," he says. Seemingly overnight, he'd turned into a technology evangelist for MEMS.

The field grew steadily throughout the 1980s. At the time Petersen's paper was published, perhaps 30 or 40 researchers around the world were working with the technology. By 1990, he estimates there were some 600. Pressure sensors for disposable blood pressure monitors and new fuel-control carburetors came on the market. The aerospace industry began using accelerometers based on MEMS. The first micromachined inkjet printheads went into mass production. A number of startups appeared, eager to run with the technology. The field got its current moniker at a 1987 National Science Foundation workshop, Petersen says.

Not surprisingly, several companies approached Petersen. He finally took the bait, joining Jim Knutti to found Transensory Devices in 1982 to develop and manufacture MEMS devices.

Leaving the stability of a corporate research job, he recalls, “was intimidating." Petersen had two young sons, so financial security was a concern. The startup's funding—just under US $1 million—eventually came from out-of-state oil, not Silicon Valley investors. “There were startups happening in Silicon Valley, but it wasn't the machine it is today. Getting funding was difficult," he says.

The team moved into a 280-square-meter fab in Fremont, Calif., and built some of their own equipment, including wafer-bonding machinery for encapsulating and protecting silicon wafers. They took contracts from bigger companies to produce samples, including light modulators like those Petersen had made at IBM. And they began developing their own MEMS devices.

“We were demonstrating a lot of devices," Petersen says, “but we weren't getting anything into production." A tire-pressure sensor for the trucking industry came close, but then the executive they'd been working with died. Not much else even approached commercialization, a problem Petersen attributes to the fact that neither he nor Knutti had manufacturing experience.

The contract work kept Transensory afloat, but Petersen wanted to get his own MEMS devices to market. It was time for startup No. 2.

In 1985, Petersen, Janusz Bryzek, and Joseph Mallon started NovaSensor, with $5 million from oil-field services giant Schlumberger. Bryzek had previously cofounded two companies that developed MEMS pressure sensors. “Janusz and his partners had the production and manufacturing DNA" that Transensory lacked, Petersen says.

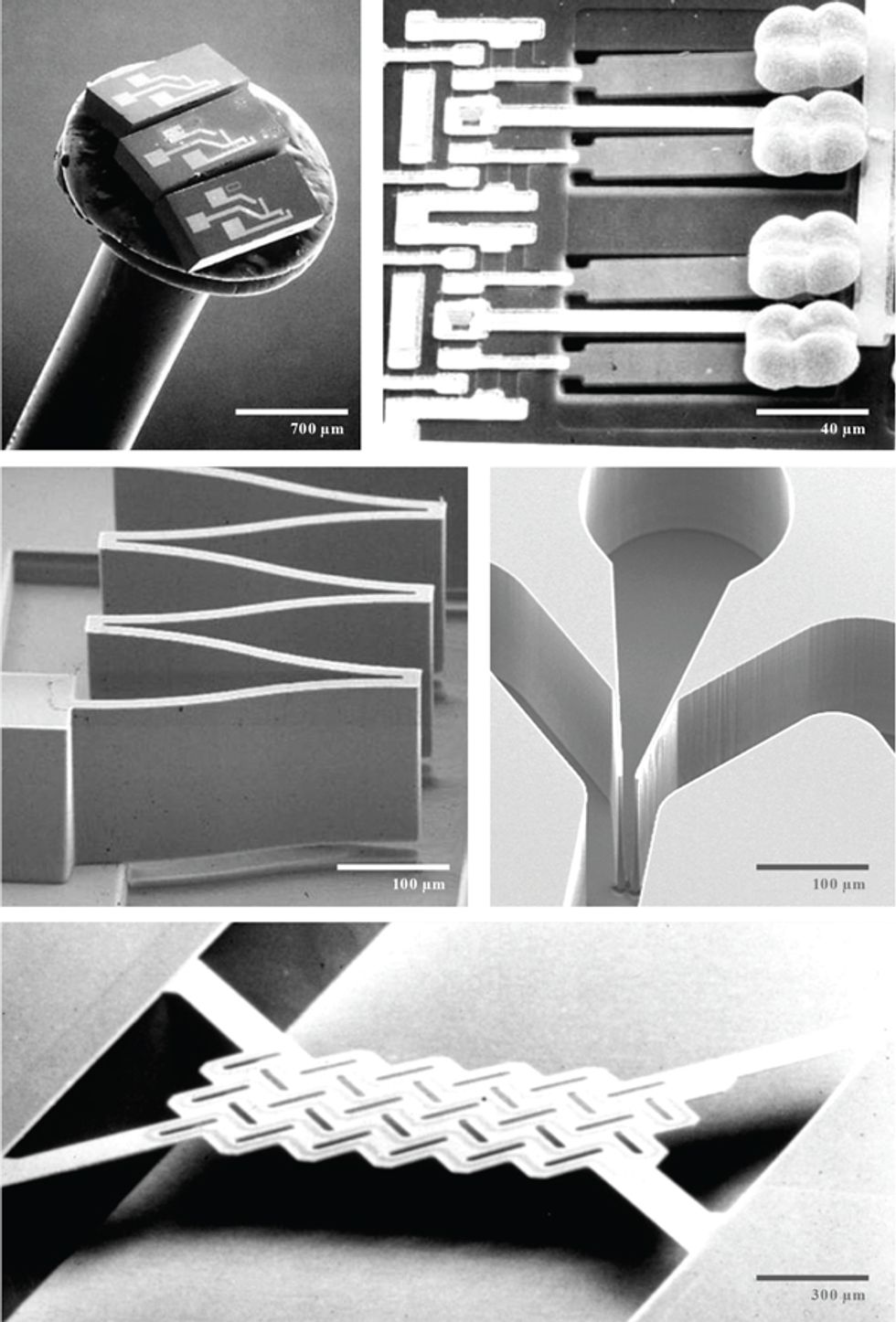

The MEMS of Mr. MEMS

Photo: Kurt Petersen

Microelectromechanical devices built by Kurt Petersen or at one of his companies include [clockwise from top left] a catheter-tip pressure sensor made with silicon fusion bonding, manufactured in about 1990 by NovaSensor; a CMOS/MEMS integrated accelerometer built at IBM Research; a prototype microfluidic structure made with deep reactive-ion etching, made in about 1993 at NovaSensor; a heated bridge element for a mass-flow sensor, manufactured in about 1984 at Transensory Devices; a leaf-spring structure made from single-crystal silicon, demonstrated in about 1993 at NovaSensor.

NovaSensor set out to build three types of pressure sensors: one for the aerospace industry, another for the oil industry, and a high-temperature pressure sensor without a specific market in mind. This last device proved to be the biggest success. It even went into the tires on the space shuttle. “We found a way to isolate the resistors from the substrate using a MEMS process. We bonded a single-crystal silicon wafer onto another oxidized wafer with pressure-sensor diaphragms, then etched away most of the top wafer, except for the resistors," Petersen recalls. He believes the sensors were the first MEMS silicon-on-insulator devices, which have since become common.

Lucas Industries acquired NovaSensor in 1991, a move that lifted Petersen high into the ranks of the “ MEMS millionaires." The NovaSensor product line is now sold by Amphenol.

Petersen stayed on for several more years to collect on his share of equity. During that time, he focused on fusion bonding, which involves etching two wafers with different patterns and then joining them together. The process allows you to create extremely intricate devices like gyroscopes. A photo of one of the first devices made with that process—it's the leaf-spring structure shown at left—appears on his business cards to this day.

By the time Petersen left NovaSensor in 1995, MEMS pressure sensors were being used in a variety of systems, including scuba diving equipment and HVAC controls, while MEMS accelerometers were beginning to appear in crash-sensing systems for automotive airbags.

Petersen didn't have anything lined up when he left NovaSensor. Allen Northrup, a researcher at the Lawrence Livermore National Laboratory, suggested to him that MEMS devices could dramatically speed up the polymerase chain reaction (PCR), a relatively new means of duplicating sequences of DNA. Bill McMillan, who worked in biotech and was a friend of Petersen's wife, confirmed the promise of PCR. So Petersen began sketching out a plan to reduce the size and cost of PCR machinery, aiming to make a handheld gadget that could be in every doctor's office.

He and Tom Gutshall had lunch at the California Café in Palo Alto. “I gave him my little pitch, and he started drawing a business plan on the paper place mat," Petersen says. He still has the place mat.

Petersen's 1982 paper had hinted at the possibilities of deep reactive-ion etching (DRIE), for creating much deeper holes and trenches in silicon than traditional chipmaking processes can. He began applying DRIE to microfluidic chips, which send tiny volumes of liquids down precise channels.

“We got the idea that we could use MEMS technology and microfluidics to heat and cool samples very rapidly, potentially making PCR so small and fast that you could use it for diagnostics in a doctor's office," Petersen says.

To commercialize the technology, Petersen and six others—including Gutshall, Kovacs, Northrup, and McMillan—cofounded Cepheid in 1996, licensing the base technology from Livermore Labs. By 1997, the company had secured $3.2 million in funding from the U.S. Department of Defense, which was eager to acquire a bioweapons detector. The first device Cepheid came up with, the Smart Cycler, used a MEMS structure to heat and cool microliters of liquids quickly and a fluorescence sensor to monitor the progress of the reaction. It wasn't a handheld gadget, but that didn't matter. It was more important to automate the PCR process.

Cepheid's next product, called the GeneXpert, aimed to make PCR even simpler. It automatically extracted the DNA from a biological sample and then added the reagents needed for the desired test.

The company went public in June 2000, just as the tech bubble was bursting. “We were one of the last companies that managed to get out an IPO" before the market dried up, Petersen says.

With cash in the bank from the public offering, the team moved the Smart Cycler into production, and as the summer of 2001 came to a close, they had shipped about 80 systems. The development of the GeneXpert was still chugging along, with the first prototype due in December 2001.

Then came the anthrax attacks. In late September and October of 2001, letters containing anthrax spores were mailed to members of the U.S. news media and the U.S. Senate, eventually infecting more than 20 and killing 5.

Cepheid had already established anthrax as one of the substances its technology could quickly detect, and the company was suddenly big news. “We were doing live PCR assays on 'Good Morning America' and on CNN with Dr. Sanjay Gupta," Petersen recalls.

The U.S. Postal Service, concerned about future biological attacks through the mail, invited anybody with biodetector technology to come demonstrate their stuff. Cepheid put its machines through the testing process in December 2001. “It went perfectly," Petersen says.

After months of additional tests, the company partnered with Northrop Grumman to build a PCR biodetector that could easily be hooked up to a mail-sorting machine. The product rolled out in 2003, and today all mail in the United States is still screened for anthrax by Cepheid machines, Petersen says. Now, the company's systems are mainly used for medical diagnostics, including strep, norovirus, flu, and chlamydia. The company sells over 20 tests approved by the U.S. Food and Drug Administration for use with Cepheid machines.

By 2003, Petersen was ready for the next thing. This time, he wanted to explore silicon resonators, devices that generate constant frequencies useful for precise timing. “I had built some of the first MEMS resonators when I was at IBM, but they weren't very good. They couldn't compete with a quartz-crystal oscillator," he says.

Three researchers—Tom Kenny, Markus Lutz, and Aaron Partridge—had figured out a better way. “These guys were making the resonator out of single-crystal silicon, and that's the world's most perfect material," Petersen says. “Polycrystalline materials shift a little bit at the grain boundaries when they get stressed. Even just an atom or two shifting over time causes changes in the mechanical properties." Single-crystal silicon doesn't change over time, but its resonant frequency does change with temperature, so the challenge was how to cancel out the temperature dependence.

Petersen, Kenny, Lutz, Partridge, and Joe Brown, a former IBM colleague who had worked with Petersen at Transensory and NovaSensor, met for yet another meal at the California Café, and drafted a business plan on yet another place mat. Robert Bosch GmbH owned some of the core intellectual property, so in addition to bringing on investors, Petersen had to convince Bosch executives in Germany to license the technology.

“I had a big meeting with their board of directors in Stuttgart," he says. “I told them, 'This is what I do. I start companies. My last one screens all the U.S. mail for anthrax.' " The board agreed not only to license the technology but also to make a major investment.

The new company, SiTime, launched in December 2004, aiming to transform the multibillion-dollar timing industry from quartz to silicon. The company shipped its first resonators in 2007. Today, its MEMS oscillators generate timing signals in mobile devices and many other electronic instruments.

Things at SiTime were running smoothly in 2008 when McMillan, one of Petersen's Cepheid cofounders, came to him with another startup idea—building an implantable continuous glucose monitor. “People had been trying to do that for 30 years, and nobody had been successful," Petersen says. Once the sensor is implanted, “the body starts walling it off with collagen, eventually preventing glucose in the blood from reaching the sensor," he explains.

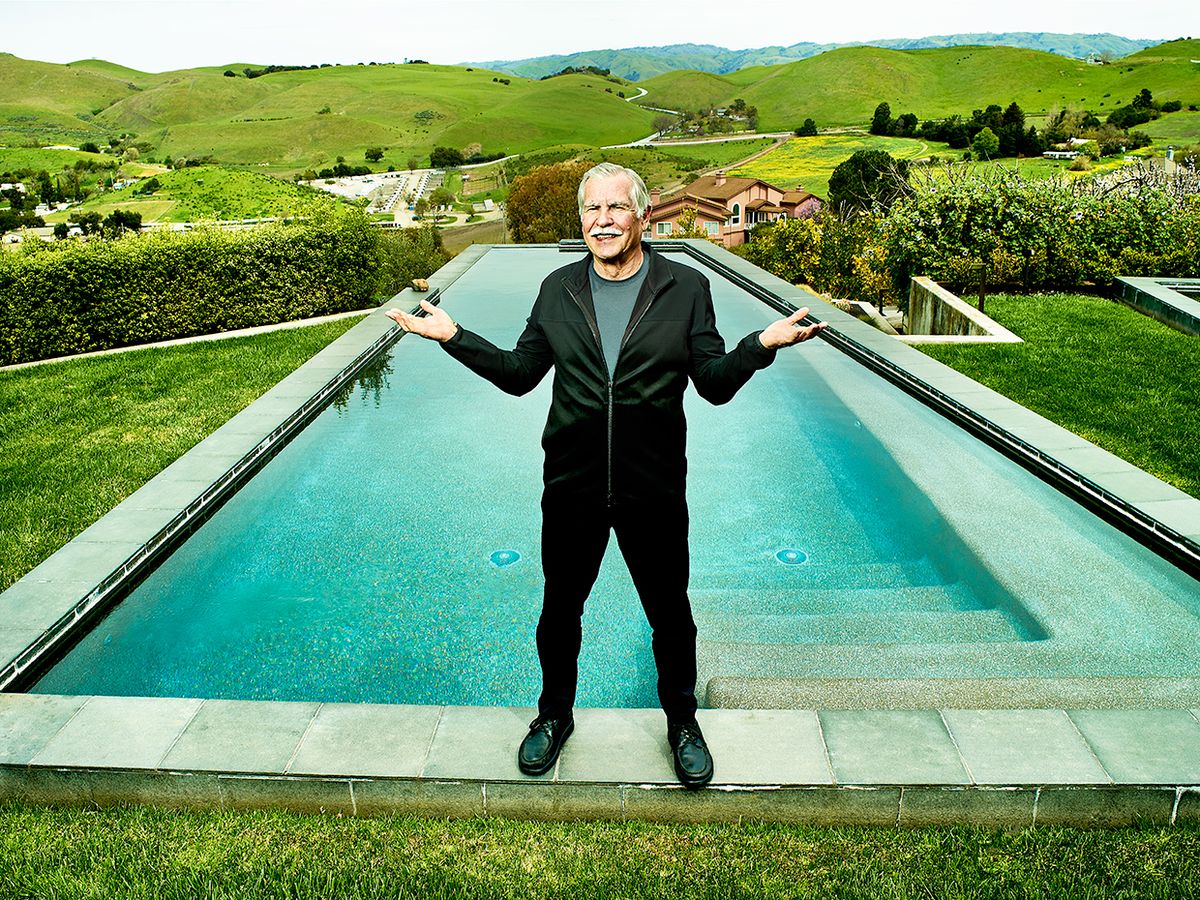

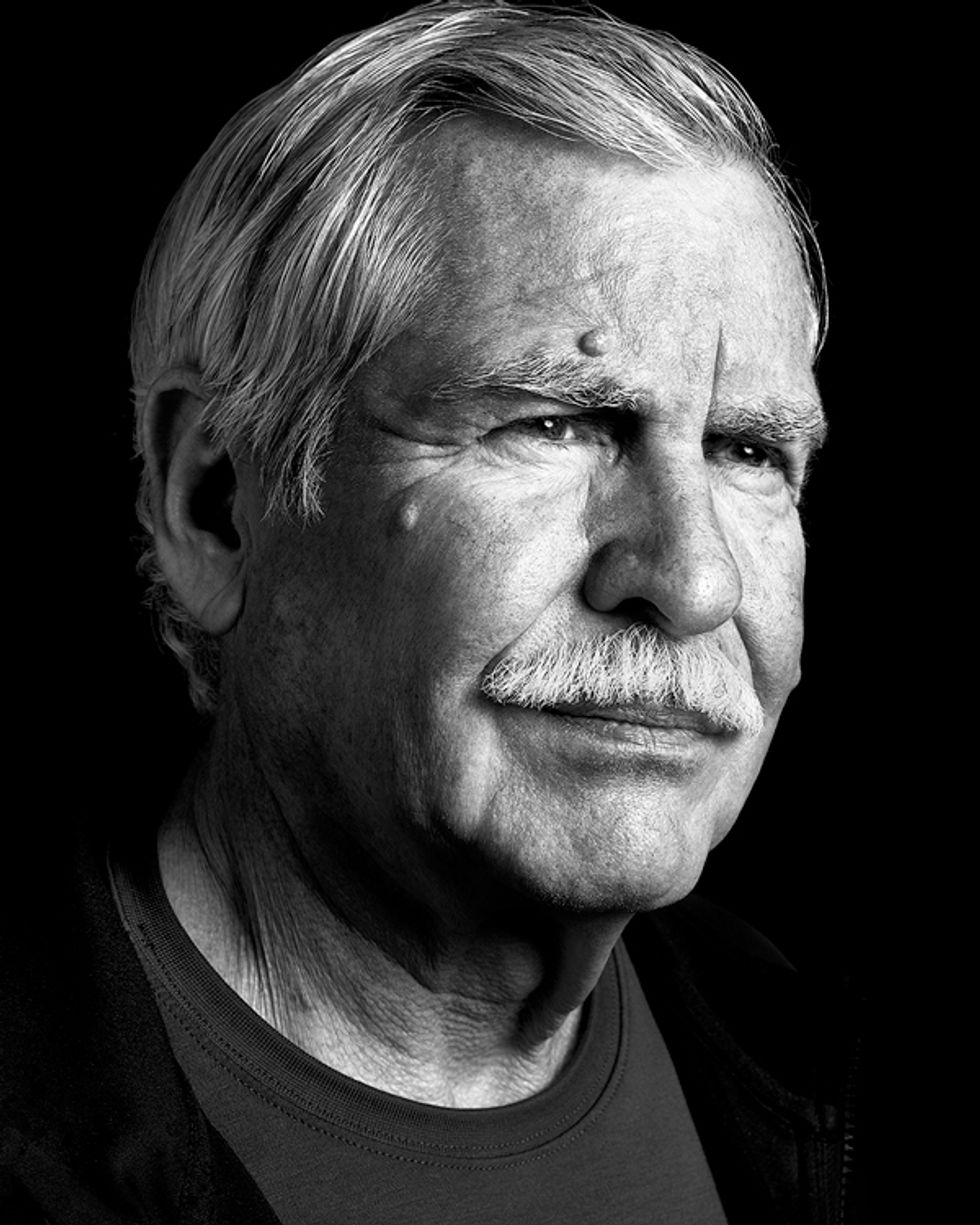

Kurt Petersen

Date of birth: 13 February 1948

Birthplace: San Francisco

Family: Wife (Carol), two adult sons (Scott and Brett)

Education: B.S. in electrical engineering, University of California, Berkeley, 1970; Ph.D. in electrical engineering, Massachusetts Institute of Technology, 1975

First job: Firefighter, California Department of Forestry and Fire Protection

First electronics job: Summer intern, Berkeley RAD Lab

Current position: Angel investor

Patents: About 40

Most recent books read: Valley of Genius (Hachette, 2018), by Adam Fisher; Bad Blood: Secrets and Lies in a Silicon Valley Startup (Knopf, 2018), by John Carreyrou

Favorite book: Sex, Time and Power (Viking, 2003), by Leonard Shlain

Favorite kind of music: 1960s and '70s dance music

Favorite Movie: Blade Runner (1982)

Pet peeve: Startups that don't respect operations

IEEE 2019 Medal of Honor citation: “For contributions to and leadership in the development and commercialization of innovative technologies in the field of MEMS"

So McMillan teamed up with Duke University researcher Natalie Wisniewski, and they came up with a solution that used a structured hydrogel to avoid the foreign-body response and a fluorescent readout to measure the concentration of glucose. Petersen went back to his optics roots to help develop the product, staying a year at the startup, Profusa. The company now has about 30 employees and $100 million in funding.

And that, Petersen says, was going to be his last full-time gig. “I just didn't want to do the day-to-day company stuff anymore. I started angel investing and that turned out to be much more fun."

Still, he couldn't resist one more team. Two Berkeley students had developed technology for MEMS filters, but they were struggling to turn it into a business. Petersen and K.G. Ganapathi joined their company, which was renamed Verreon, and Petersen served as CTO, helping to coordinate the company's sale to Qualcomm in 2010.

It was Petersen's third go-around as CTO or the equivalent. In all his startups, he claimed the CEO title only once, at SiTime. “At NovaSensor, two of the other guys wanted to be president," says Roger Grace, a marketing consultant who worked with the company. “Kurt didn't care. He took the CTO title. He's not an ego-driven guy."

“There's not one person in the MEMS world that has anything other than wonderful things to say about Kurt, because he is just so kind, thoughtful, and helpful," says Grace. “There are a lot of smart guys, but he is unique because he is so humble. Being around him is like putting on your favorite pair of slippers."

Ganapathi agrees. “It's not often that you find someone who has been as successful as Kurt has and is so universally liked," he says.

These days, Petersen is back to angel investing, targeting MEMS companies along with medical devices and biotech. He says he's invested in about 70 companies, and nearly half have turned out to be successful, reaping a 350 percent return on his investments. That's an impressive track record. According to a recent study, a more typical return for a long-term angel investor with a broad portfolio is 250 percent.

“The guy has an uncanny ability to smell out what can be a product. It can be 3 or 15 years down the road, but he's got a nose for it," says Ganapathi.

Petersen joined the Silicon Valley Band of Angels in 2012, an invitation-only group of about 200 investors who meet regularly to hear pitches and share information. He now cochairs the Band's hardware subgroup. He also serves on the boards of two companies and as a mentor at a dozen others. He meets in person with several of his advisees every day, keeping in touch with those at Canadian and East Coast companies by phone.

At 71, Petersen does not see retirement on the horizon. “The entrepreneurs are energetic and motivated and ambitious, and it's too much fun to be around them," he says.

This article appears in the May 2019 print issue as “The Marvelous Mr. MEMS."

This article was updated on 25 April and 1 May 2019.

Tekla S. Perry is a former IEEE Spectrum editor. Based in Palo Alto, Calif., she's been covering the people, companies, and technology that make Silicon Valley a special place for more than 40 years. An IEEE member, she holds a bachelor's degree in journalism from Michigan State University.