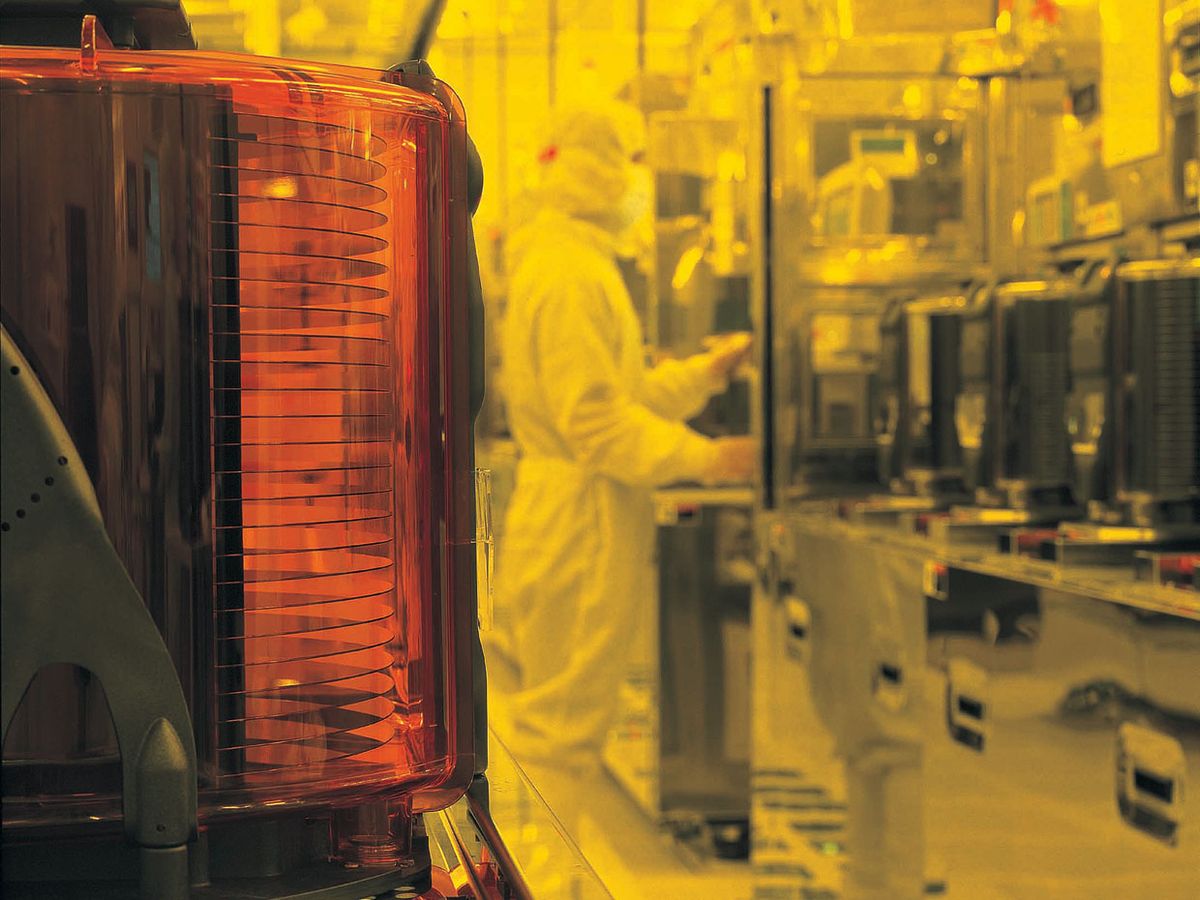

The 3-D transistor is poised to go mainstream. After falling behind Intel, the world’s biggest foundries are all gearing up to produce these cutting edge switches. And to accelerate the process, some have opted to take an unusual step: marrying the new transistors with an older approach to building the wiring that ties them together on a chip.

The hope is that this hybrid strategy will help foundries make 3-D transistors, or FinFETs, available to most of the world’s semiconductor firms by 2014, a good year earlier than anticipated. That could help close the gap with Intel, which unveiled the first commercial 3-D transistor process in 2011 and likely aims to supply the technology, with few exceptions, only to itself. Intel plans to release the transistors in smartphone and tablet chips tailor-made to compete against the foundries’ customers.

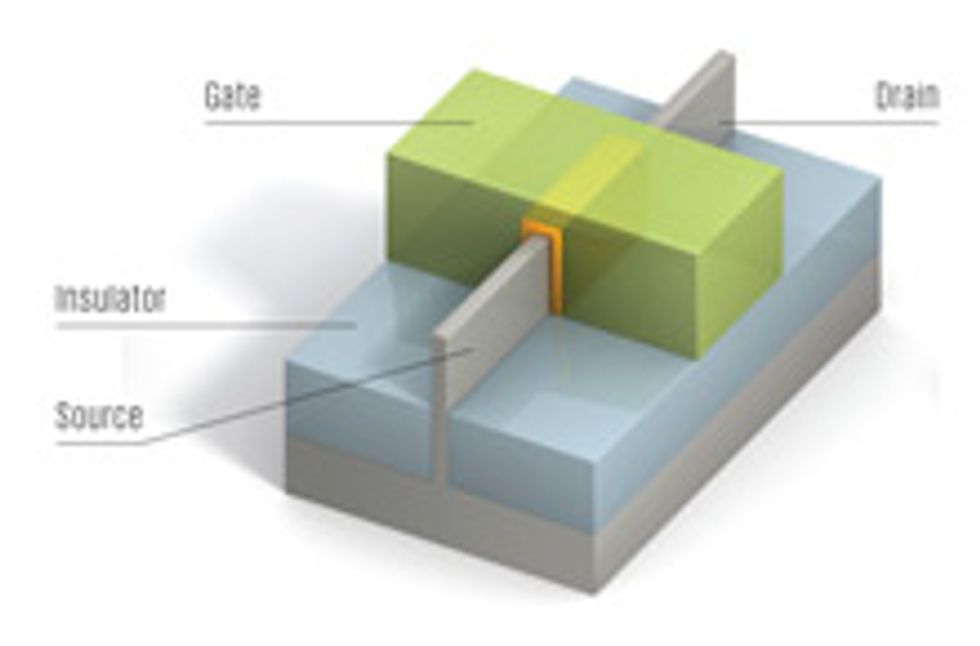

Chipmakers are switching to FinFETs because each time they have shrunk their ordinary, planar transistors, manufacturers have seen a smaller performance gain. FinFETs—which effectively turn the transistor’s current- carrying channel on its side to create a fin—carry more current and leak less of it, making for circuits that perform better and use less power. GlobalFoundries, Samsung, Taiwan Semiconductor Manufacturing Co. (TSMC), and United Microelectronics have all made it clear that they plan to pursue the technology. They aim to introduce FinFETs at the 14-nanometer-manufacturing-process node—a step, more or less, behind Intel’s 22-nm introduction.

To get there, both GlobalFoundries and TSMC have revealed they’ll take a half step. They will replace planar transistors with a denser array of FinFETs, but they won’t advance the manufacturing process used to build the wiring that connects the devices on the “back end” layers of the chip. As a result, although there will be more transistors in any given area, a good number of them won’t be connected and therefore can’t be used. The chips won’t be much smaller than the 20-nm generation, which is going into production now. That means the foundries won’t be able to create more of them on a single wafer to reduce costs. Nonetheless, GlobalFoundries expects the chips it will produce could be as much as 55 percent faster or 40 percent less power hungry than the 20-nm generation.

For GlobalFoundries, the advantage of this halfway approach is that it will let the company keep more than 7000 design rules that were developed for the 20-nm planar chip, while changing just 60 or so that are needed to describe the fin, says Subramani Kengeri, vice president of advanced technology architecture at GlobalFoundries. “First- generation FinFET is a huge challenge. There’s no question about it,” says Kengeri. “Adding more risks to that by adding other complexi ties that were not necessarily fin- related was not prudent.” All told, the hybrid approach should allow the company to accelerate production by a year.

TSMC, which calls its FinFET scheme a 16-nm process, says its chips are “similar” in size and density to other foundries’ 14-nm offerings. Later this year, both TSMC and GlobalFoundries hope to create small batches of test chips for customers and are targeting full production in 2014, which will put the companies’ releases more or less on the same schedule as that of Intel’s own 14-nm chips.

“I think this incremental strategy is probably a very sound, safe way of not changing too many things at the same time and developing something they can be sure can be production worthy,” says Chi-Ping Hsu, who heads up research and development for the Silicon Realization Group at Cadence, an electronic design automation firm based in San Jose, Calif.

FinFETs are “a huge challenge for the whole industry,” Hsu says. He estimates that his team at Cadence has already spent some 4000 man-years overhauling computer code for today’s generation of chips so that processor operation can be simu lated in a realistic time frame. FinFETs, which boast stronger electrical effects on their neighbors and have dimensions that can’t be adjusted, are an added challenge. Hsu reckons it will cost the foundries and their partners some US $6 billion to develop the manufacturing prowess and the computational tools needed to make 14-nm and 16-nm chips.

Whether the investment will pay off in the end is unclear, says Sam Tuan Wang, chief analyst for semiconductor foundries at Gartner. “People say if Intel can do it, I can do it. That’s not true,” he says. We may not have to wait long to find out.

This article originally appeared in print as "3-D Transistors for All."

Rachel Courtland, an unabashed astronomy aficionado, is a former senior associate editor at Spectrum. She now works in the editorial department at Nature. At Spectrum, she wrote about a variety of engineering efforts, including the quest for energy-producing fusion at the National Ignition Facility and the hunt for dark matter using an ultraquiet radio receiver. In 2014, she received a Neal Award for her feature on shrinking transistors and how the semiconductor industry talks about the challenge.