All the amazing carbon-nanotube logic circuits we’ve heard about over the years have a dirty secret: Some of those nanotubes are metallic rather than the semiconducting type that’s wanted. This tiny fraction of bad tubes is no big deal for logic circuits. They add a bit of noise, but nothing the digital nature of logic can’t deal with. The problem has been analog circuits.

For analog, that stray metallic nanotube may as well be basilisk venom. “A single metallic [carbon nanotube] causes a complete circuit failure in a simple amplifier,” Aya G. Amer explained to engineers at the IEEE International Solid-State Circuits Conference last week in San Francisco. Amer and her colleagues in the MIT laboratory of Max Shulaker have found a way to solve that problem, creating the first carbon-nanotube mixed-signal ICs .

Their solution hinges on the 3D integration of carbon-nanotube field-effect transistors (CNTFETs) and resistive RAM memory (RRAM), a technology Shulaker helped pioneer with H.-S. Philip Wong and Subhasish Mitra while at Stanford University. [The trio describe a path to carbon-nanotube-based computers in "Computing With Carbon Nanotubes," IEEE Spectrum, July 2016.]

The process involves depositing carbon nanotubes on a layer of already produced silicon circuits, processing these to form transistors and their interconnections, and then building RRAM atop this stack. This is not something that can be done using layers of silicon electronics, because the process temperatures involved would destroy the metal interconnects. Even stacking preprocessed silicon chips can’t match it, because those chips have a limited ability to make vertical connections. The vertical interconnects in the Stanford/MIT method can be made thousands of times as dense, boosting interlayer bandwidth.

The U.S. Defense Advanced Research Projects Agency is so keen on the technology that it’s pouring US $61 million into an effort to develop the manufacturing process at SkyWater Technology Foundry, in Bloomington, Minn.

The analog process starts by building essentially the same style of CNTFET needed for logic. That’s basically a metal gate buried beneath a channel made of many horizontally aligned carbon nanotubes that stretch between a source and drain electrode. At least one of these nanotubes is likely to be metallic; the trick is to isolate it and take it out of any future circuit. To do that, Shulaker’s team broke the source electrode into three pieces. Statistically, only one of these would be connected to a metallic electrode.

In order to determine which one and remove it from the circuit, they integrated a RRAM cell atop each of the drain electrodes. RRAM holds data in the form of resistance. Flow current in one direction and the resistance increases. Flow it in the other direction and it decreases. So they applied a voltage across the circuit comprising the RRAMs and the nanotubes. For the two with semiconducting connections, this had no effect; no current could flow because the transistor’s gate was not energized. But for the one hiding the metallic nanotube, things were quite different. The metallic nanotube acted as a short circuit across the transistor, pouring current through it and its attached RRAM cell. That caused the RRAM cell’s resistance to leap to a value so high that it effectively cut off the path containing the metallic nanotube. So when the transistor is actually used in a circuit, only the semiconducting pathways count.

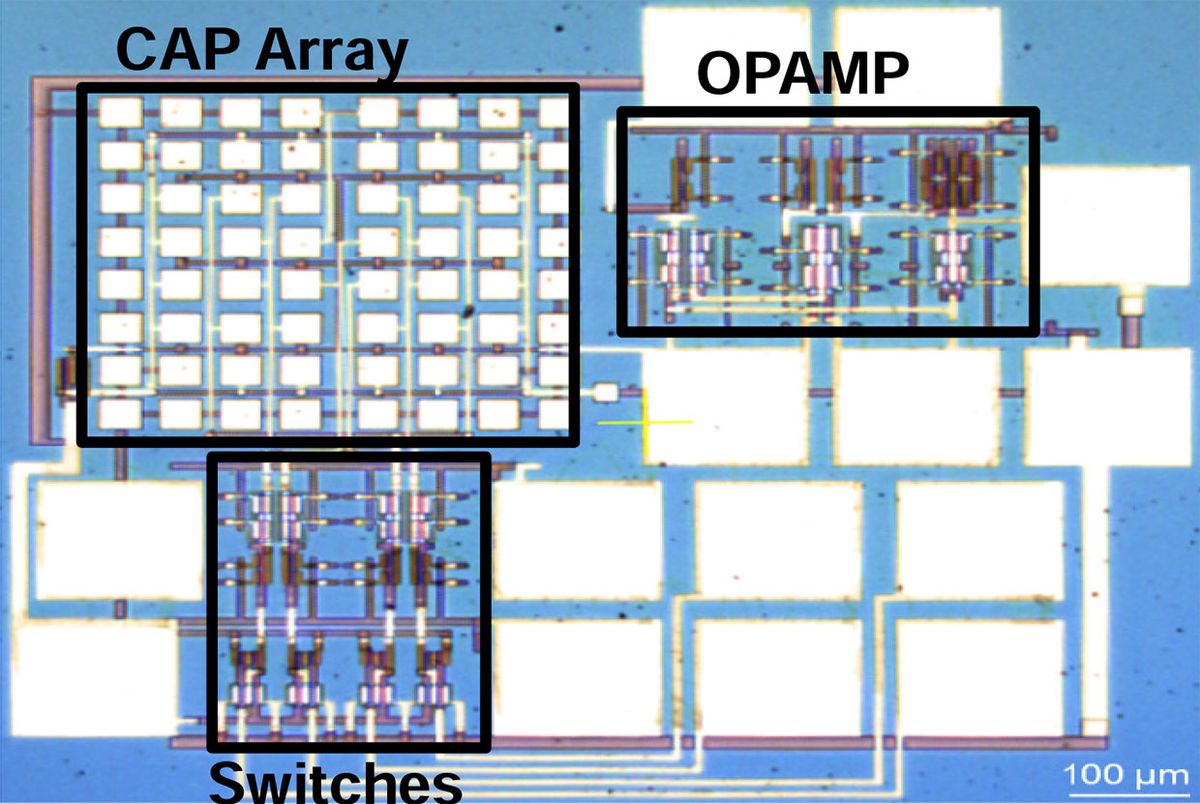

Amer and Shulaker call the process “self-healing analog with RRAM and CNFETs” (SHARC); it’s self-healing in that the transistor removes its own flaws. The team built two mixed-signal circuits that used SHARC in the analog parts, a 4-bit digital-to-analog converter and 4-bit analog-to-digital converter. With 306 CNFETs, the latter is the largest CMOS carbon-nanotube circuit reported to date.

The SHARC technology “ties in nicely with a bunch of things we’re doing,” including the SkyWater project, says Shulaker. “The DARPA program is about computing, and there’s more to computing than just” digital logic.

Samuel K. Moore is the senior editor at IEEE Spectrum in charge of semiconductors coverage. An IEEE member, he has a bachelor's degree in biomedical engineering from Brown University and a master's degree in journalism from New York University.