Fremont, Calif.-based magnetic RAM startup, Spin Memory, says it has developed a transistor that allows MRAM and resistive RAM to be scaled down considerably. According to the company, the device could also defeat a stubborn security vulnerability in DRAM called Row Hammer.

Spin Memory calls the device the “Universal Selector.” In a memory cell, the selector is the transistor used to access the memory element—a magnetic tunnel junction in MRAM, a resistive material in RRAM, and a capacitor in DRAM. These are usually built into the body of the silicon, with the memory element constructed above them. Making the selector smaller and simplifying the layout of interconnects that contact it, leads to more compact memory cells.

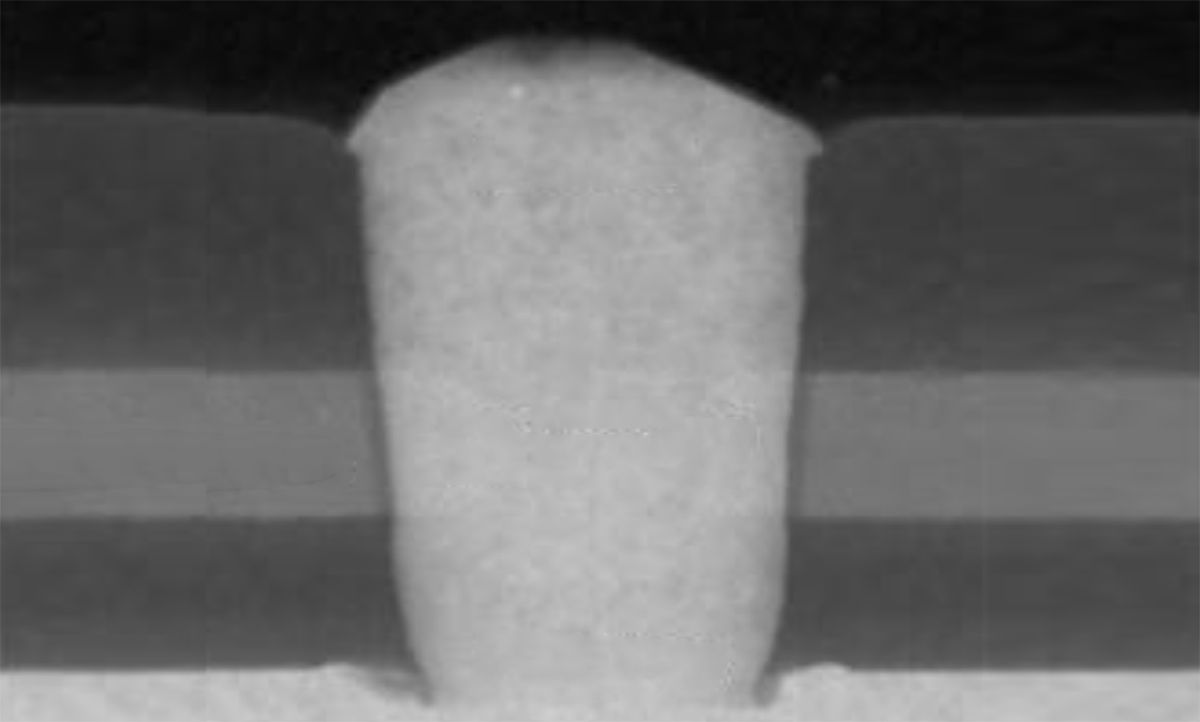

Essentially, transistors are built horizontal to the plane of the silicon. When the device is on, current flows through a channel region between a source and drain. The Universal Selector tilts that geometry 90 degrees. The source is at bottom attached to a conductor buried in the silicon, the channel region is a vertical silicon pillar, and the drain is on top. The gate, the part of the device that controls the flow of charge, surrounds the channel region ion all sides.

Such vertical gate-all-around devices are similar to those used to make today’s multilayer NAND flash storage chips. But Spin Memory’s devices span only one layer and are tuned to operate at much lower voltages.

According to the company, the vertical device would improve DRAM array density by 20-35% and allow manufacturers to pack up to five times more MRAM or RRAM memory into the same area.

The selector is part of a trio of inventions Spin Memory is developing to boost MRAM’s adoption. The other two are an improved magnetic tunnel junction, and a circuit design that boosts MRAM’s endurance and read and write speeds, as well as eliminating sources of error. The combination, according to Jeff Lewis, senior vice president of product development, would bring MRAM to a level of performance on par with SRAM, the superfast memory embedded in today’s CPUs and other processors.

“The use of SRAM as the main on-chip memory is becoming problematic because of its known scalability,” says Lewis. Because it’s just a single transistor and a magnetic tunnel junction, MRAM could one day have a density advantage over SRAM, which is made up of six-transistors. More importantly, unlike SRAM, MRAM keeps its data even when there is no power to the memory cell. Right now, however, MRAM cells are considerably larger than SRAM. “One of our key objectives was to come up with a smaller cell size for MRAM so that it could have greater attraction as an SRAM replacement.”

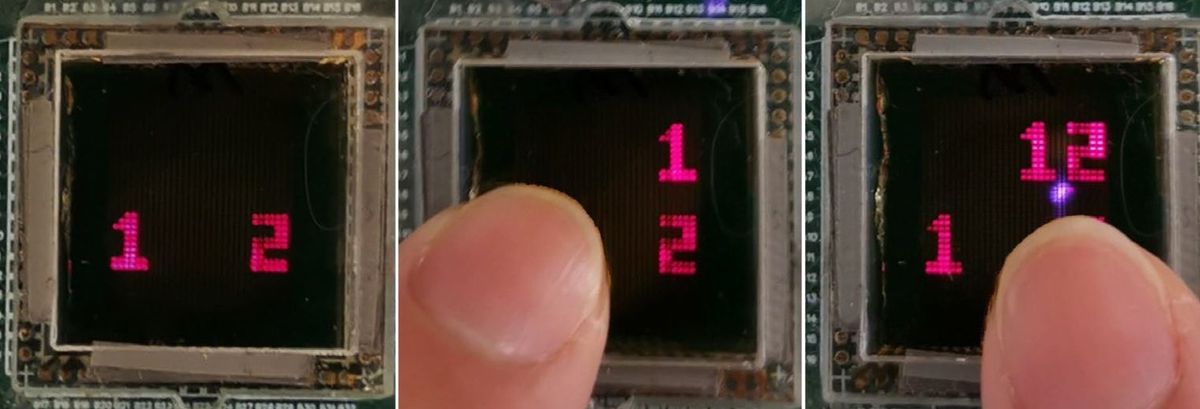

With DRAM, the main memory of choice for computers, the Universal Selector has an interesting side-effect: it should make the memory immune to the Row Hammer. This vulnerability occurs when a row of DRAM cells is rapidly charged and discharged. (Basically, flipping the bits at an extremely high rate.) Stray charge from this action can migrate to a neighboring row of cells, corrupting the bits there.

“Row hammer is one of the leading issues in DRAM reliability and security, and has long been a frustrating plague on the memory industry. As DRAM’s longstanding major disturb problem, row hammering is only becoming more of a problem as cells shrink,” Charles Slayman, a device reliability expert at Cisco Systems, said in a press release.

According to Lewis, the new device is immune to this problem because the transistor channel is outside of the bulk of the silicon, and so it’s isolated from the wandering charge. “This is a root-cause fix for row hammer,” he says.

For use in DRAM, the device would have to be shrunk down considerably, which possible. But improving MRAM is the immediate goal. That will involve optimizing the strength of the drive current and other aspects of the device. Spin Memory engineers will be presenting details of Universal Selector next week at the 31st Magnetic Recording Conference.

Samuel K. Moore is the senior editor at IEEE Spectrum in charge of semiconductors coverage. An IEEE member, he has a bachelor's degree in biomedical engineering from Brown University and a master's degree in journalism from New York University.