Hot on the heels of the debut of Intel’s 3-D transistor, the semiconductor firm SuVolta has announced they’ve come up with a competitor.

The California-based start-up was in stealth mode until today, when the company announced a new platform called “PowerShrink”, which modifies the design of planar transistors to reduce power consumption.

SuVolta says the new design will be ideal for cell phones, tablet computers, and other mobile devices. And unlike the two leading alternative transistor designs – 3-D and silicon-on-insulator (SOI) (see our interview with FinFET co-inventor Chenming Hu to get a run-down on both) – SuVolta says its approach will require few changes to the manufacturing process.

“For the last 15 years people only talked about FinFET and SOI,” says SuVolta CTO Scott Thompson. “We’re suggesting there is a third option. I think anywhere you care about cost and power, SuVolta will win over those two technologies.”

Unlike Intel, SuVolta doesn’t make transistors itself. Instead, the company hopes to license the designs to third parties. Its first customer is Fujitsu, which aims to use the technology in chips that use 65nm transistors starting next year. (Intel, for reference, is now beginning production on its 22nm node).

SuVolta says its transistors consume half as much power when run at the same speed as ordinary planar transistors, but it’s not yet clear how this is done. Thompson told me that the company’s process modifies the channel of the transistor to include an upper layer that does not contain dopants – the non-silicon atoms that are scattered in silicon to alter its electronic properties. Other layers of the channel contain dopants that are placed with “near atomic-level control”, Thompson says.

If the exact number and position of dopants can be fixed, that could tamp down variation in a number of transistor properties, most notably the threshold voltage – the voltage that needs to be applied to a transistor gate to allow current to flow through the channel.

Indeed, SuVolta reports they’ve managed to cut the variation in threshold voltage in half. That reduces the amount of power transistors need to draw in order to perform switching operations, since there is less uncertainty in how well any given transistor will perform.

“They’re making the behavior of the transistors more predictable,” says Tom Halfhill, an analyst at The Linley Group who was briefed by SuVolta. But fully evaluating SuVolta's approach might have to wait. “We don’t really know what materials they’re changing or how they’re changing them. All they’re describing is the effect it has,” Halfhill says.

Still, given what's known so far, Halfhill says, the technology looks promising. He estimates it might take Intel's competitors four years before they'll be able to start mass production of FinFET transistors. SuVolta's design could help shorten that performance gap while companies play catch-up.

But could SuVolta's approach ultimately compete with FinFETs and SOIs, particularly at the scale of the smallest transistors? SuVolta says they anticipate the technology could be useful down to the 14nm transistor node.

The scheme could make 65nm SuVolta transistors work as well as 45nm transistors, says Dean Freeman, an analyst at Gartner. But based on the data SuVolta has released, Freeman says, it’s unclear whether the approach will give the same sort of power gains at 14nm that that firm sees at 65nm.

Even if SuVolta's design won't be useful at small scales, the new approach could still extend the life of larger transistors that are still in wide use. Whether it will take off will depend on whether the benefits of "PowerShrink" outweigh the gains companies get by shrinking transistors down to pack more of them onto chips, one of the main ways that chipmakers reduce costs. “Companies will need to perform a cost benefit analysis to see if the improvement in power is worth the cost of a redesign, or if a shrink is more advantageous,” Freeman says.

That question makes it hard to predict how widely SuVolta's design will ultimately be adopted. Although SuVolta's ranks include Intel and Silicon Valley venture capital veterans, the firm’s “challenges are as daunting as its pedigree," notes EETimes. "The company must pioneer a business model initially focused on selling intellectual property to fabs, a new kind of sale to customers more accustomed to buying capital equipment.”

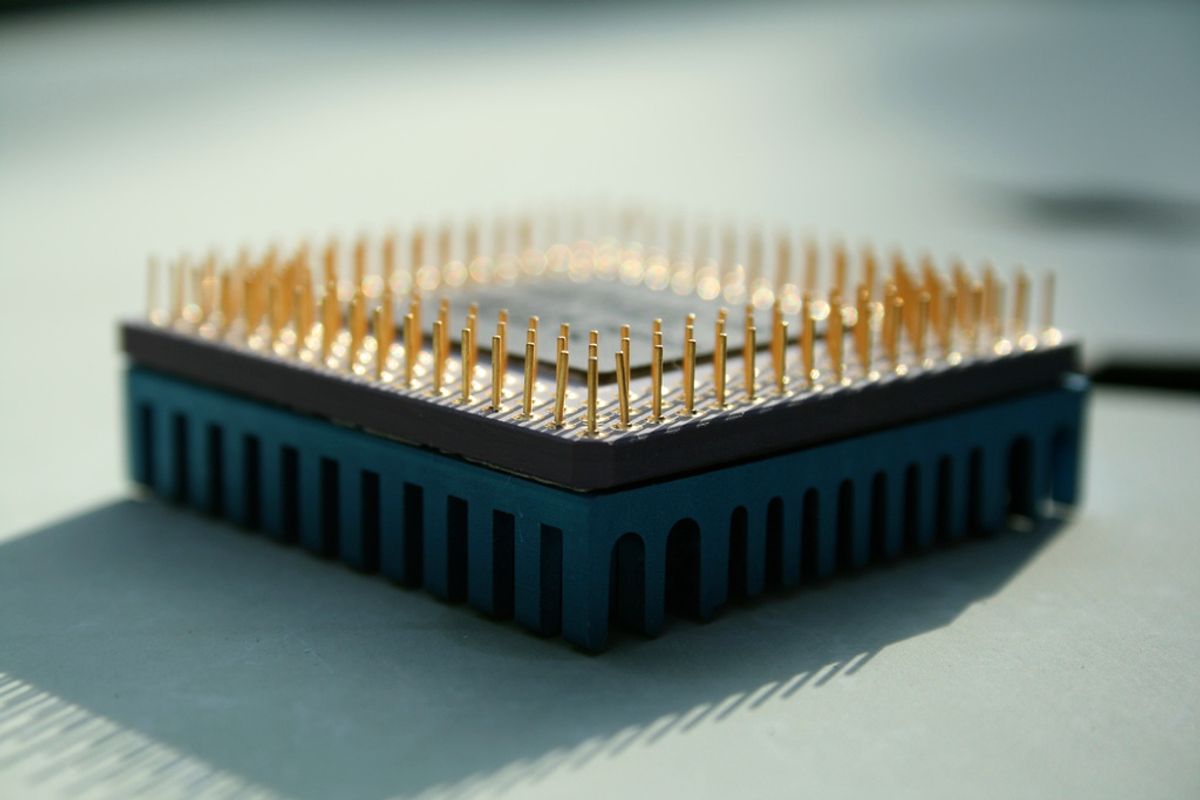

(Image: Gary Huston)

Rachel Courtland, an unabashed astronomy aficionado, is a former senior associate editor at Spectrum. She now works in the editorial department at Nature. At Spectrum, she wrote about a variety of engineering efforts, including the quest for energy-producing fusion at the National Ignition Facility and the hunt for dark matter using an ultraquiet radio receiver. In 2014, she received a Neal Award for her feature on shrinking transistors and how the semiconductor industry talks about the challenge.