Using only two materials and a room temperature process, researchers in Korea have made extremely simple thin-film transistors on a plastic sheet. The transistors could pave the way for cheap, disposable flexible electronics, the researchers say.

Thin-film transistors are used today to turn pixels on and off in flat-panel displays. They are generally made of amorphous silicon deposited on rigid glass.

The new flexible transistors are made of indium oxide, which belongs to a class of materials known as amorphous oxide semiconductors. Amorphous oxides boast better electrical properties than amorphous silicon. Researchers believe that, compared to amorphous silicon, amorphous oxides could make for smaller, more energy efficient transistors that switch quickly. That would translate to sharper, faster displays. Plus, amorphous oxides can be cheaply printed on plastic.

Researchers in Tokyo first reported transistors made of amorphous indium gallium zinc oxide (IGZO) in 2004. Now, many big display manufacturers are working on LCD and OLED displays that use oxide transistors to drive their pixels.

The research team at Sungkyunkwan University in Korea has come up with an ultra-simple transistor design and fabrication method that could further cut the cost of amorphous oxide devices, because the process requires less material and fewer processing steps.

Transistors generally have three parts: a thin film semiconductor channel, a gate dielectric, and the electrodes (source, drain and gate). These three parts are formed from at least three different materials using three different processing steps.

The new transistors use just two materials: indium oxide and an ion gel. Ion gels are relatively new materials consisting of conductive ionic liquid trapped inside a polymer matrix.

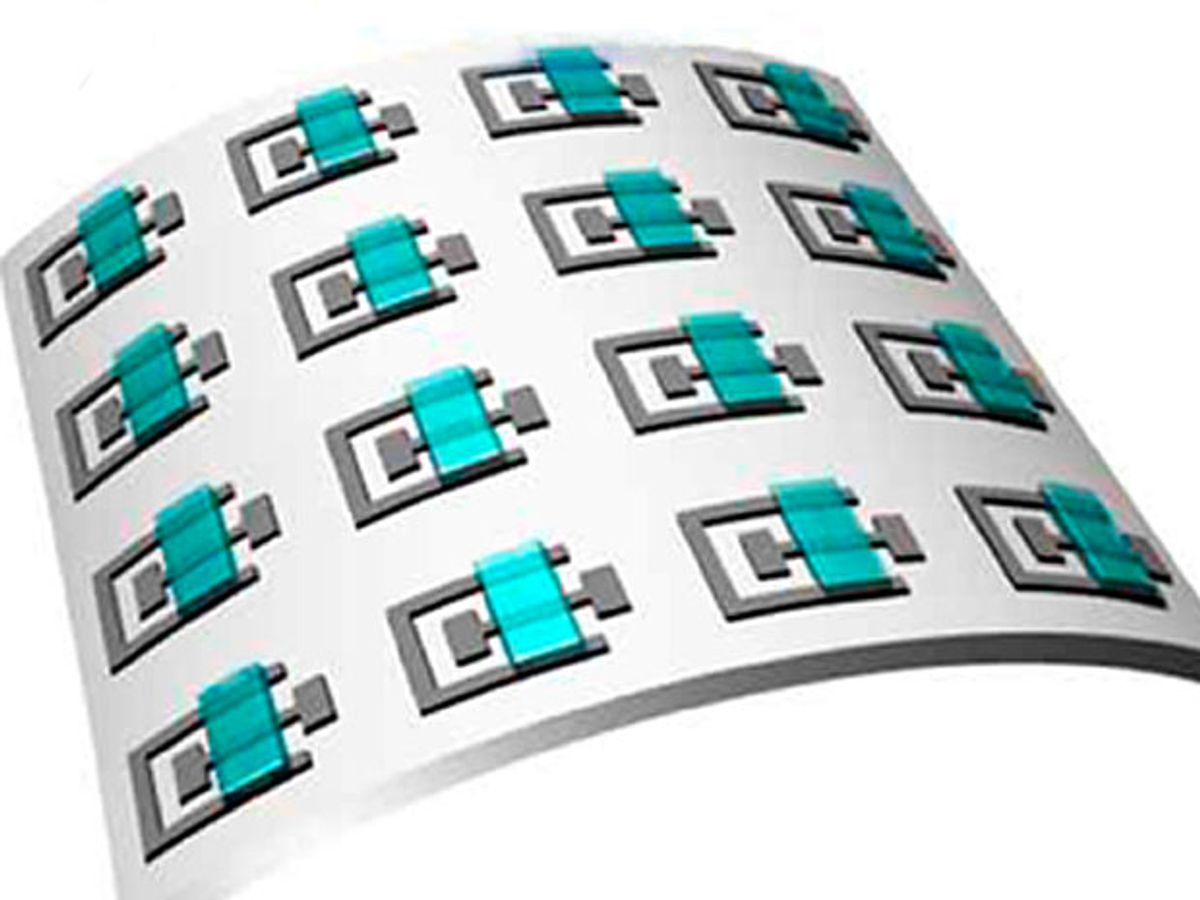

The researchers first deposit indium oxide on a plastic sheet. They pattern it to produce patches of a U-shaped indium oxide layer surrounding a barbell-shaped indium oxide layer. Then they deposit the ion gel across the arm of the barbell so that it touched the ends of the U. Finally, they expose the sheet to argon gas, which metallizes all the indium oxide surfaces except the ion gel-covered barbell arm.

The plastic sheet is now coated with an array of transistors. In each transistor, the metallized U-shaped indium oxide acts as the gate electrode, the metallized barbell ends serve as the source and drain, and the gel-coated barbell arm acts as the semiconductor channel. The ion gel is the gate dielectric.

As a proof-of-concept, the researchers demonstrated a NOT logic circuit made of two transistors. The NOT device, or inverter, is the basic building block of digital electronics.

The method could be used with other oxides such as indium zinc oxide and IGZO, the researchers say. They reported their findings in the journal ACS Nano.

- Printing Electronics Directly on Delicate Surfaces—Like the Back of ... ›

- Organic Thin-Film Transistors' New Gate Dielectric Opens Door to ... ›

- Laser-printed polysilicon transistors on paper - IEEE Spectrum ›

Prachi Patel is a freelance journalist based in Pittsburgh. She writes about energy, biotechnology, materials science, nanotechnology, and computing.