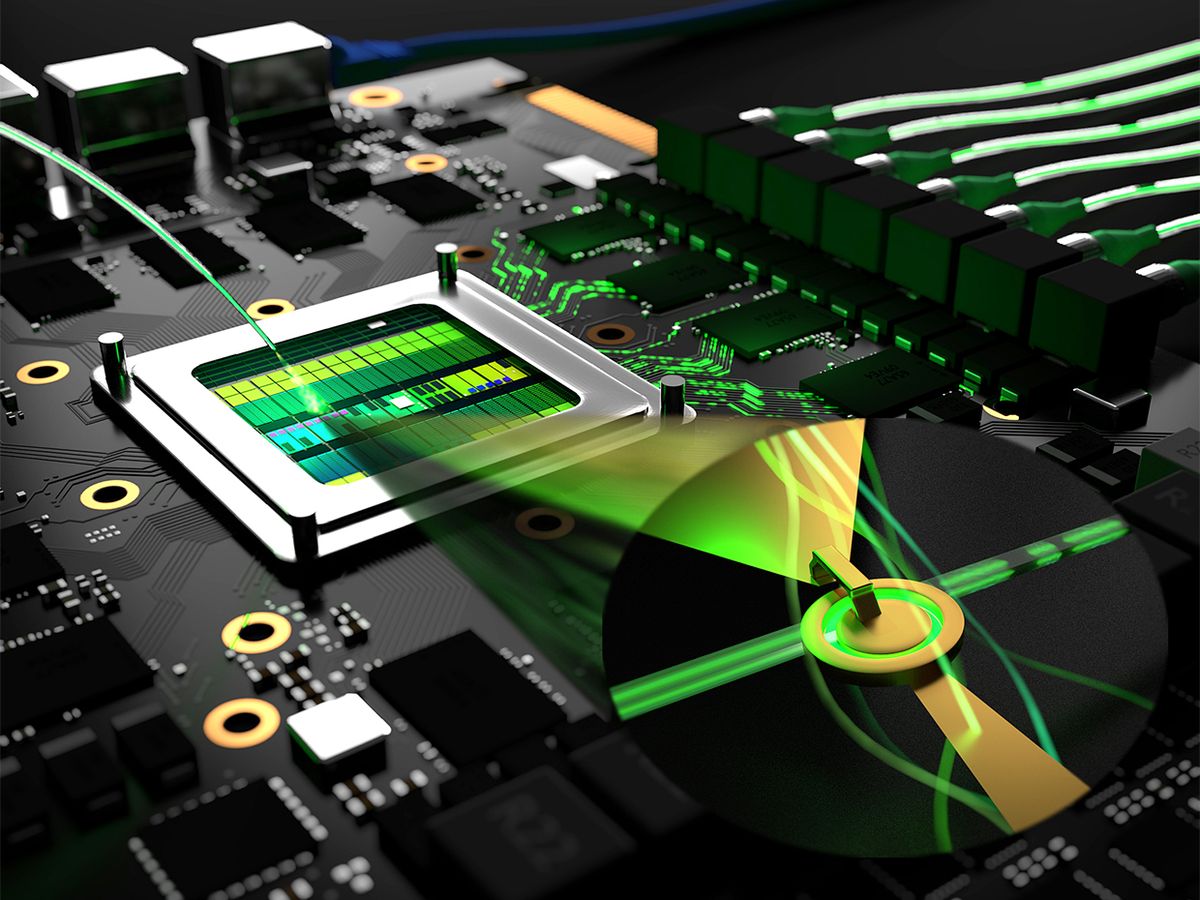

While the field of plasmonics may sound esoteric, it is based on some fairly straightforward physics and, when applied to devices, could alter photonics dramatically. It involves exploiting the waves of electrons—known as surface plasmons—that are triggered when light (photons) strikes a metal surface. The length of these plasmon waves is much shorter than the wavelengths of light, making it possible to use light indirectly in the very small dimensions of today’s integrated circuits.

By transforming wavelengths of light into waves of electrons, it has become possible for scientists to merge the speed of optics with the dimensions of electronic devices. However, plasmonics has remained mired in a proof-of-concept state despite many practical devices having been experimentally demonstrated for on-chip circuitry.

Now, an international team of researchers has developed a switch for plasmonic devices that could eventually lead to a CMOS-compatible material platform for making practical plasmonic circuits.

In research described in the journal Nature, researchers at Purdue University in collaboration with those from ETH Zürich, the University of Washington, and Virginia Commonwealth University, have created a switch in the form of a ring modulator for a plasmonic-based circuit that uses resonance—or a vibration—to control whether photons interact with surface plasmons, or not. This switch should overcome a key problem for these circuits: the light used within them can be absorbed by surface plasmons—a property known as “loss.”

In the on-state mode, the resonator resonates at a wavelength different from that of the signal (light) wave, according to Alexandra Boltasseva, a professor at Purdue University, who was a co-author of the research. In this mode, the signal wave does not couple into the resonator, and passes through a silicon waveguide without losses.

In the off-state mode, the refractive index of the polymer in the ring is changed. Now the ring resonates at the same frequency as the source signal, and the light moves into the resonator, where plasmonic losses dampen the resonance of the resonator.

“One of the challenges in the field of plasmonics is the ohmic losses [losses from resistance] of the metals, which typically give the impression that any plasmonic device is bound to be very lossy,” said Boltasseva. “In our research, we show that by clever engineering, these losses can be bypassed, or even used to our advantage.”

For this device, the on-state mode is purely photonic—meaning it’s not based on a plasmonic effect—resulting in low loss. In the off-state mode, it is plasmonic.

The next step in the research, according to Boltasseva, will be to make similar devices using CMOS-compatible materials that have optical properties similar to those of gold, and which are durable, stable at high temperatures, and cheap.

Boltasseva added: “Making fast and efficient electro-plasmonic modulators out of titanium nitride will be the next big step in developing practical plasmonic circuits integrated with silicon photonic devices.”

Dexter Johnson is a contributing editor at IEEE Spectrum, with a focus on nanotechnology.