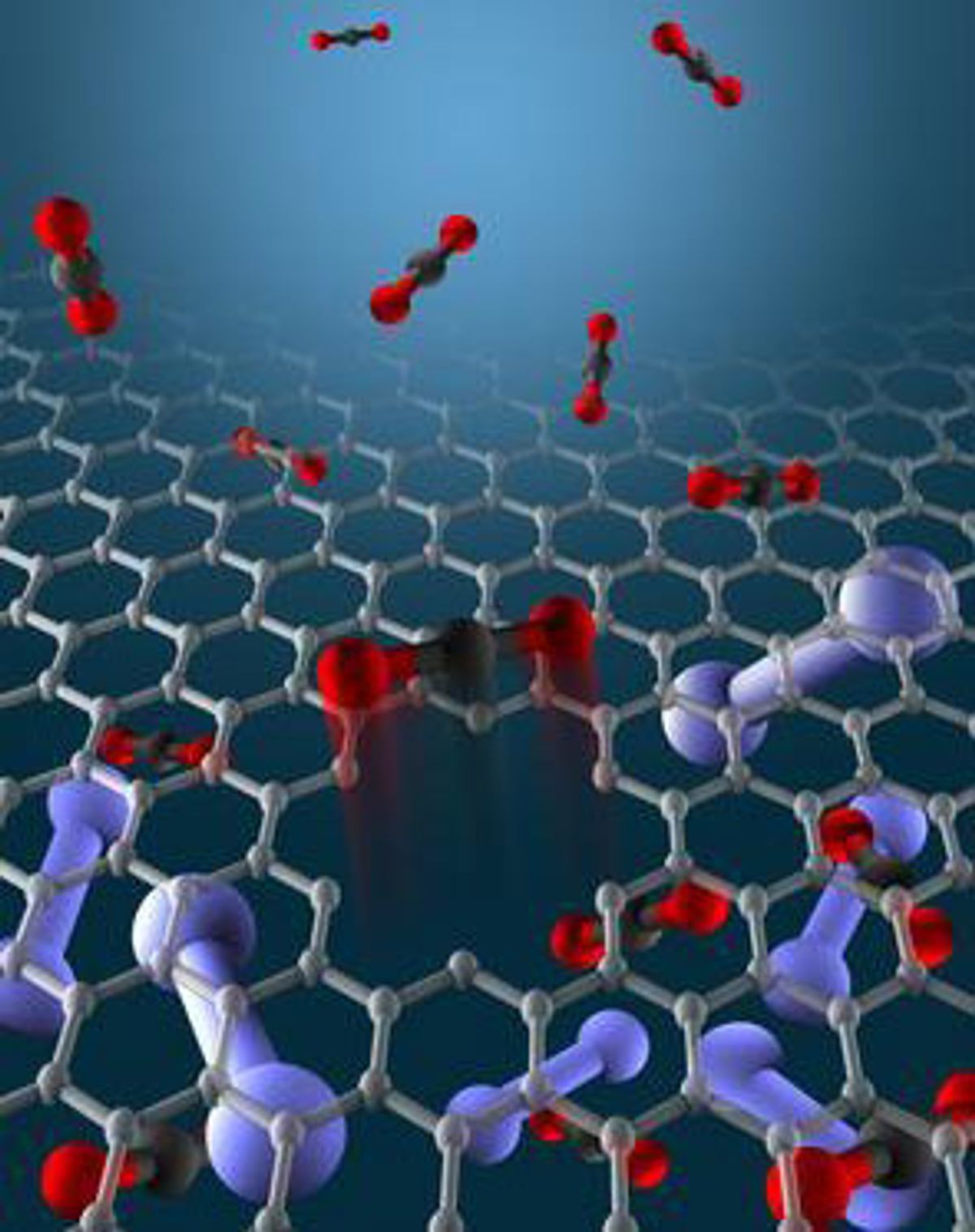

The Univ. of Colorado research builds on work that was completed last year at Boulder that showed that graphene possessed extraordinary adhesion capabilities. That work demonstrated that if graphene were used in a multi-layer membrane, the adhesion between the layers of the membrane would be extremely strong.

This most recent work also seems to go one step beyond research at MIT from earlier this year. In that work, scientists used computer simulation to show that nanoporous graphene could replace membrane materials currently used in the reverse osmosis water desalination processes. At the time, the MIT researchers said they expected that turning their computer models into real world membranes would be daunting. According to the researchers, getting the pores size precisely right would be difficult to do on a large scale.

While the Boulder researchers have not attempted to scale up their experimental results yet, they have managed to get the pore size correct on the graphene so it can separate a variety of gases.

The research, which was published in the journal Nature Nanotechnology (“Selective molecular sieving through porous graphene”), was able to achieve its precisely sized pores by etching them into graphene sheets with a process involving ultraviolet light-induced oxidation. The resulting porous graphene was then tested on a range of gases including “hydrogen, carbon dioxide, argon, nitrogen, methane and sulphur hexaflouride -- which range in size from 0.29 to 0.49 nanometers.”

“These atomically thin, porous graphene membranes represent a new class of ideal molecular sieves, where gas transport occurs through pores which have a thickness and diameter on the atomic scale,” says Colorado mechanical engineering professor Scott Bunch in a university press release.

The main technical challenge, according to the researchers, will be bringing these results up to an industrial scale. In particular, they will need to find a process by which they can create large enough sheets of graphene. The researchers even concede that getting the pores precisely defined still needs further development.

Dexter Johnson is a contributing editor at IEEE Spectrum, with a focus on nanotechnology.