Fast Films

New insulators will save us from the “dirty little secret” that threatens Moore’s law

So Far, so good. Semiconductor makers have been on a roll for three decades, shrinking transistors to improve chip performance—and their bottom line. Today, state-of-the-art chips have transistors roughly a micrometer in overall length; dozens of them could perch on top of a human red blood cell. But this very success has brought the chipmakers to the brink of a steep, new obstacle to further gains in performance.

At the crux of the problem are the tiny metal wires that weave the transistors on today’s chips into integrated circuits. In the most advanced ICs, transistors switch up to 10 billion times a second, and their metal interconnects can barely keep up. The narrower the wire, the longer it takes a signal to propagate along it. And each new generation of chips only makes matters worse: while interconnect delay times are stretching out, transistor switching is getting faster, sending more signals down slow lines.

It’s the semiconductor industry’s dirty little secret, and it threatens the seemingly immutable Moore’s Law, namely, that transistor density and hence chip performance will periodically double. No one knows how a disruption in this prediction would affect the industry; but not many are on record as predicting a happy outcome. With billions of dollars at stake, researchers worldwide have stepped up their efforts to find a way around the problem.

The good news is that the industry thinks it is zeroing in on a solution: change the propagation characteristics of those tiny on-chip transmission lines. But as one might expect, chipmakers are not agreed on a single approach. Rather, two are on the table, each championed by heavy hitters in the field [see table].

What they are after is not unfamiliar. Engineers have been shortening the delay for several years, by simply reducing the line’s so-called time constant, which is equivalent to the product of its resistance and capacitance. Resistance was lowered around 1998, when IBM Corp. (Armonk, N.Y.) and Motorola Inc. (Schaumburg, Ill.) began replacing aluminum interconnects with copper.

Now the line’s capacitance is being lowered by changing the material that insulates it from the surrounding silicon chip as well as from neighboring wire. The capacitance depends on a property of the insulator known as its dielectric constant. So researchers are developing thin films that have a lower dielectric constant, or lower k , than the silicon dioxide insulating layer used most commonly up to now.

A solution will be lucrative: the market just for low-k precursors, the starter chemicals with which certain low-k films are made, will be worth as much as US $400 million annually by 2006, according to market research firm Kline & Co. (Little Falls, N.J.). That projection takes into account the fact that the International Technology Roadmap for Semiconductors calls for all chips having wiring widths of 90 nanometers and below to be made with some sort of low-k dielectric film.

The bad news is that these low-k films are extremely difficult to integrate into semiconductor manufacture. They are soft, weak, and adhere poorly to both the silicon and the metal wire. Not nearly as tough as silicon dioxide, they don’t withstand conventional processing and crack and delaminate easily.

As a result, last year low-k dielectrics were used in only a few 130-nm chips. The real action starts later this year, when chipmakers will try to use the new materials in 90-nm chips.

“At this point,” says Gartner Dataquest principal analyst Dean Freeman in San Jose, Calif., “everybody starts to come on board with a low-k process. There’s no way around it.” The next generation of 65-nm chips will require even lower-k films that are even more challenging to process.

Low-k saves the day

A material’s k value measures the extent to which it concentrates an electric field. The capacitance between two conducting plates (in this case between the interconnect and the substrate or between two neighboring interconnects) decreases as the k of the insulator between the two plates gets smaller. Air is the ultimate low-k material, with a k of 1.00059.

Silicon dioxide, the industry’s workhorse dielectric, has a k of 4.2. That’s just not good enough for chips that pack more wires in smaller spaces. The latest 130-nm Pentium 4 processor, in production now at Intel Corp. (Santa Clara, Calif.), has 55 million transistors and uses roughly 4.8 km of interconnects to support each square centimeter of its circuitry. When 90-nm microprocessors reach the street this year, they will house twice as many transistors and nearly 6.9 km of interconnects per square centimeter.

Such close packing turns interconnects into tiny charge-storing systems—in other words, into capacitors, points out Kevin Martin, associate director of Georgia Institute of Technology’s Microelectronics Research Center (Atlanta). The ability of a capacitor to store a charge is determined not only by the k-value of the insulator, but the distance between adjacent wires both horizontally, on a chip layer, and vertically, between that layer and the one above it. “The closer the wires [in both dimensions], the greater the capacitance and the longer it takes for the signal to propagate down the line,” he explains.

Chipmakers began moving to lower-k dielectrics in 1997, when they added fluorine to the silicon dioxide to form fluorosilicate glass. At 3.6, the k of this glass was better than silicon dioxide’s 4.2, but future chips will require a k below 3.0. Most chipmakers use fluorosilicate glass in their 130-nm ICs. A handful, including IBM, United Microelectronics, Fujitsu, and Sony, introduced chips featuring low-k films in 2002.

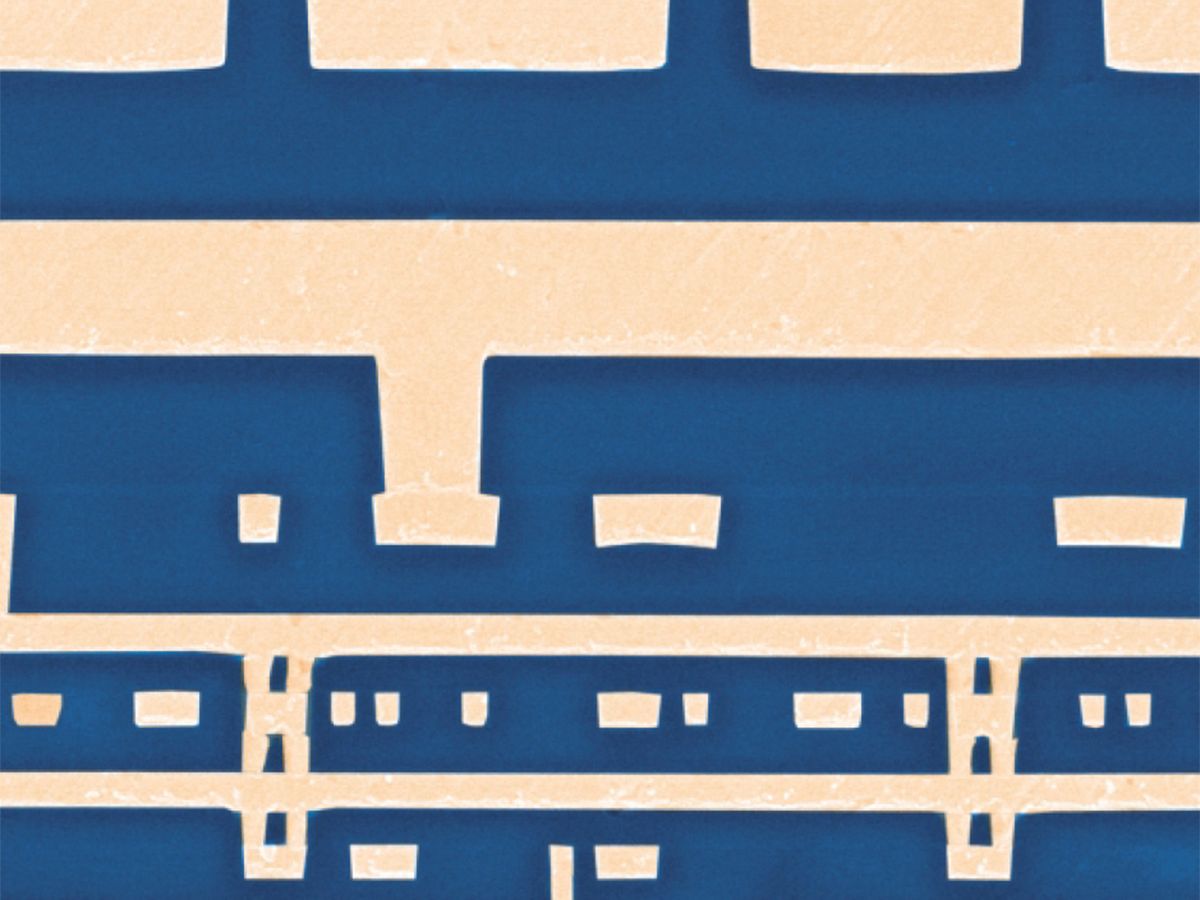

Companies that embrace low-k could in the future reap major cost benefits. Chips have transistors near the substrate and several interconnect levels above [see photo]. Low-k dielectrics allow designers to cram interconnects closer together and so fewer layers are needed to hold them all.

“If a company sticks with FSG [fluorosilicate glass] instead of low-k, it will need one or two more levels of metal to achieve similar performance,” Freeman explains. By eliminating them, a company could save $50-$150 million in capital equipment costs per chip plant.

Particles versus polymers

Not only are low-k materials difficult to integrate, but the specific challenges vary with the type of material. Right now, the industry is torn between very different visions of a low-k future.

On one side are technologies that rely on chemical vapor deposition, or CVD. Examples are Coral from Novellus Systems Inc. (San Jose, Calif.) and Black Diamond from Applied Materials Inc. (Santa Clara, Calif.), both leading suppliers of chip-making equipment.

Used for decades to deposit silicon dioxides in ordinary chips, CVD thermally cracks large molecules into smaller parts that reassemble as thin films on the semiconductor surface. Its strengths are industry familiarity and users’ freedom to modify the films by adjusting operating conditions, changing precursors, and adding gases.

Lowdown On Low-k Processes

The proprietary Coral and Black Diamond dielectrics are made by adding carbon to the silicon dioxide recipe in a CVD process that yields carbon-doped oxide [see illustration]. This insulator achieves k values down to 2.8-2.9, low enough for 130-nm chips. By adding still more carbon to the recipe, Novellus and Applied Materials expect next-generation products, such as Black Diamond II, to reach a k of less than 2.7, which appears good enough for 90-nm chips.

The alternative technology departs from silicon dioxide and vapor deposition entirely and relies on spin-on dielectrics. These are carbon or silicon-based polymers (chains of smaller molecules called monomers) applied by pouring liquid mixtures onto rapidly spinning wafers.

SiLK, from Dow Chemical Co. (Midland, Mich.) and the leading contender, has demonstrated a k of 2.6. More importantly, Dow says SiLK provides a path to a k below 2.2, good enough for 65 nm in 2005-06 and perhaps even 45 nm in 2008-10.

The catch is that spin-on dielectrics can achieve these low values only if they are made porous. Porous films are like sponges, absorbing the chemicals used to process chips, with the (unfortunate) potential for re-emitting them later in the process. Furthermore, they are extremely fragile. No company has ever made a chip from porous materials, nor has any metrology company found a way to measure their properties. Chip manufacturers that chose to buy into spin-on dielectrics would have to reinvent their entire chip-making process.

Both alternatives raise imposing barriers. The success of either will hinge on the resolution of the materials issues surrounding both CVD and spin-on.

Can CVD handle the stress?

Chipmakers with billion-dollar plants would really prefer to stay with CVD. But to their chagrin, the new materials used for the films are difficult to process, says Reinhold Dauskardt, a professor of Materials Science and Engineering at Stanford University in California. He has seen countless films torn apart by stresses within the chip during fabrication.The problem is that CVD systems substitute carbon in the form of methyl groups for silicon in oxide. This creates a more open structure—think of it as pseudoporosity—which lowers the film’s k but also weakens its mechanical properties.

Chipmakers create most of the IC structure at a temperature of 400-450 °C. When the chip starts to cool, however, its materials, including its silicon substrate, copper interconnects, and dielectric films contract at different rates. This generates enormous stresses that cause the weakest layer—the low-k dielectric—to fail, says Dauskardt.

Low-k CVD films can also be vulnerable to chemical mechanical polishing (CMP), in which a rotating head and slurry of fine abrasive particles grind away excess copper at each level of construction. As the chip rises level by level, the polishing leaves behind copper interconnects running through trenches in the dielectric. Early attempts to grind away combinations of copper and low-k dielectric shredded the dielectric, yanked the copper out of the trench, and peeled off entire layers of interconnects.

Makers of the polishing tools responded by reducing or even eliminating abrasives and using more chemicals for removal, as well as lowering the force on the rotating head. Yet only Applied Materials (and Dow on the spin-on side) claim their low-k films withstand direct polishing. Most other chipmakers deposit hard silicon carbide or silicon nitride over the soft low-k films prior to applying copper. This protects the dielectric from abrasion, but increases k values and adds costly processing steps.

Dauskardt notes that most conversations about low-k processing at technical conferences revolve around mechanical and thermal issues. How those issues play out will determine whether vapor deposition or spin-on becomes the platform of the future.

Evolving options

“Early on, the thinking was that spin-on films would have the lowest low-k values,” admits Meggy Gotuaco, Applied Materials’ global product manager for CVD low-k products. “It is now fairly clear CVD can be extended and used for at least two more generations of chips, to 90 and 65 nm.” For instance, Motorola will launch its first 130-nm Black Diamond chip (with a k of 2.8-2.9) in early 2003. For its 90-nm chips, the company has penciled in Black Diamond II, with a k of between 2.5 and 2.7.

Chipmakers that go with carbon-doped oxide at 90 nm have options beyond Applied Materials’ Black Diamond and Black Diamond II. ASM International NV (Bilthoven, the Netherlands) says its Aurora low-k carbon-doped oxide is currently being evaluated on both 130- and 90-nm pilot lines.

Novellus’ Coral was the first carbon-doped oxide to reach market when Trident Microsystems Inc. (Sunnyvale, Calif.) began sampling its XP4 laptop 3D graphics processor in April 2002. The XP4 uses six Coral layers followed by two layers of fluorosilicate glass at the upper levels where interconnects are spaced further apart. The XP4 can generate a billion pixels per second at less than 3 W, more than twice the pixels per watt of competitors that use twice as many transistors.

Gartner’s Freeman and Mike Corbett of market researcher Kline & Co. believe CVD films will dominate the 90-nm generation of chips, but remain skeptical that CVD can produce usable carbon-doped oxide films with a k below 2.5 for 65-nm chips, around 2006. low-k CVD films, with a k down to 2.0, have been produced by making the layers porous, but at the cost of sharply reduced hardness, as is the case with the Orion dielectric from Trikon Technologies Inc. (Newport, UK).

“While companies have demonstrated those values in films, the question is whether they can do that in an integrated stack [of IC layers],” Freeman says. “Whenever you add more carbon, you create more problems—cracking, softness, lack of adhesion.”

Revolution in the making

That could leave spin-on as the 65-nm solution. At 130 nm, SiLK from Dow has been the only spin-on dielectric with traction in the market, though JSR Microelectronics (Tokyo) and Honeywell Electronic Materials (Sunnyvale, Calif.) offer their own versions.

The polymeric SiLK is very different from the glassy films produced by vapor deposition. SiLK is much weaker and softer than any CVD low-k , but it can absorb stresses without failing, in the way a plastic ball bounces off the floor while a glass ball shatters. And because SiLK is so much tougher than carbon-doped oxide films, it will absorb more punishment from chemical mechanical polishing before it fails.

According to Applied Materials and Novellus, spin-on systems will cost up to three times as much as all-CVD systems. CVD systems, they argue, not only apply the dielectric layers in a single machine but virtually all the materials needed to build a wafer. Spin-ons, in contrast, shuttle wafers between CVD chambers and spin-on and bake equipment, which drags out the process.

Freeman doesn’t think this shuttling need be a problem. “Most lines are already mixed with CVD and spin-on photoresist equipment [used in photolithography],” he notes. He maintains that the CVD chambers could also be used to deposit other materials on the IC, such as the barrier layers that protect interconnects from chemical attack. The result could actually be an increase in production capacity, he says.

Victor Wang, who heads Motorola’s 90-nm team, believes spin-on is already cost competitive in new facilities. With the industry planning to invest in new fabs as it migrates to larger, 300-mm-diameter wafers over the next five years, he says that now might be an ideal time to consider spin-on systems.

Dow’s vision is still bolder. It sees spin-on materials as ultimately replacing most if not all films now applied by CVD and other deposition processes. First, though, it faces the sobering challenge of convincing the industry that it should put its faith in porous dielectrics.

Surface value

Dow believes that creating pores in SiLK to enlarge its surface will lower its k to 1.8 and, eventually, to 1.6. If Dow could deliver usable porous films, its customers could retain the same materials and process flow from 130 nm and 90 nm to 65 nm and perhaps even to 45 nm.

Porous materials lower the film’s average k by adding nanoscale pockets of air. Happily, spin-on chemistry lends itself to pore formation because chemists can attach pore-forming materials, or porogens, to dielectric polymers before spinning them onto the wafer. They then heat the mixture, which turns the porogens into gases that diffuse out, leaving empty spaces behind.

Porosity creates huge challenges, not the least of which is knowing what you’re getting, says John Iacoponi, low-k program manager for the semiconductor manufacturing research consortium, International Sematech (Austin, Texas). No one has a proven, economical way to determine subsurface pore size, density, and location. If pores are too close together or too large, producers won’t know until the films crack or delaminate.

This leaves chipmakers with some tough decisions. While CVD-based carbon-doped oxide films work at 90 nm, further k -value reductions will leave them more brittle and less adhesive. And while spin-on films also appear ready for 90 nm, the porosity needed for 65 nm and below poses challenges.

Perhaps new materials will save the day. Intel, for one, has worked with xerogels, gossamer-like silica films that contain 90 percent air. Silicon Valley start-up Dielectric Systems Inc. (Fremont, Calif.) says it has sold its first CVD system to deposit solid polymeric films with good mechanical strength and k of 2.2.

It is also possible that companies will be able to extend existing low-k materials simply by improving their understanding of the fundamental properties of ever-thinner films, says Stanford’s Dauskardt. As films get thinner, the surface properties of the materials and how the surfaces interact with one another come increasingly to dominate the physical characteristics of the ICs. “A lot of the work to reduce stress revolves around designing structures that have reliable interfaces,” he observes.

Such concern for interfaces may unsettle an industry that until recently measured interfacial adhesion by pressing down Scotch Tape and seeing if a film could be lifted off. Motorola’s experience analyzing and engineering copper and fluorosilicate interfaces greatly simplified its transition to Black Diamond, says Wang.

“It comes down to how you engineer the interfaces, and the problem grows more pronounced as you scale down,” he explains. Because Motorola understood interfacial behavior, it knew how to change its design rules to prevent cracks and delamination during thermal cycling.

Although Motorola sees Applied Materials as a likely partner for 90-nm chips, Wang also has programs with other vendors of carbon-doped oxides. ASM International is one of them. It uses oxygen-containing starting molecules that are different from the methyl-based precursors used by Applied Materials and Novellus. He also likes JSR’s porous silicon-based polymers, and says SiLK is cost-effective now. If he had to make a bet, Wang would put his money on spin-on for 65 nm and below. But he admits that CVD may also find a way to get there.

The rest of the industry, after nearly three decades of working with silicon dioxide, is doing the same thing: keeping its options open.

To Probe Further

Read the semiconductor roadmap at https://public.itrs.net/Files/2002Update/2002Update.pdf [PDF].

Meet Dow Chemical’s SiLK consortium at https://www.silknetalliance.com.

Learn about Applied Material’s Black Diamond at https://www.appliedmaterials.com/products/cvd_low_k.html.