In 2013, a team at Stanford reported that it had arranged arrays of tiny, atom-thick cylinders to create an entirely new machine: the world’s very first carbon nanotube computer. With a clock speed of just 1 kilohertz and fewer than 200 transistors, it didn’t stand a chance of competing with today’s silicon-based processors.

Now, the gap between silicon and carbon nanotubes is starting to narrow. In two papers, presented in December at the IEEE International Electron Devices Meeting in San Francisco, the same team has shown they can make carbon nanotube transistors with current densities and other properties that rival similarly sized silicon transistors. Graduate student Max Shulaker also reported that the team could build carbon nanotube transistors directly on top of silicon circuits.

“Now that we have this nanotube that’s on par with conventional silicon,” says H.-S. Philip Wong, who led the work along with Shulaker’s advisor, Subhasish Mitra, “we can think about building high-performance systems.”

Unlike its two-dimensional cousin, graphene, the carbon nanotube can be a natural semiconductor, and it’s long been eyed as a potential material for speedy and energy-efficient switches.

In practice, however, creating transistors with enough carbon nanotubes to carry a sizable amount of current has proved a bit tricky. Growing carbon nanotubes results in a mix of metallic and semiconducting forms, which is undesirable, and the number of nanotubes must be made quite uniform from transistor to transistor in order to get any power and performance benefits.

In prior work, the Stanford team solved the metallic-nanotube problem by designing circuits that could vaporize metallic tubes, leaving only the semiconducting ones behind. Now they’ve refined the fabrication process to boost the density of carbon nanotubes while preserving the level of uniformity.

Their fabrication process begins with quartz, on which the carbon nanotubes are grown. A layer of gold is deposited on top and then peeled away with thermal tape, taking the nanotubes with them. The nanotubes can then be transferred to the target surface, where the thermal tape is eased off and the gold chemically removed, leaving an array of parallel carbon nanotubes on the surface.

One transfer yields around eight nanotubes per micrometer, as measured perpendicular to the direction that current would flow across the devices. But in this latest work, the team showed they could repeat this deposition process more than a dozen times by laying down a gluelike polymer before each successive deposition of carbon nanotubes. The polymer prevented the carbon nanotubes from sticking to one another and becoming a spaghetti-like mess when exposed to the liquid used to etch away the gold. It also helped smooth the surface for the next layer of nanotubes.

With this approach, the team was able to make transistors with an average density of 100 carbon nanotubes per micrometer, giving a current density of up to 122 microamperes per micrometer.

This is neither the highest density of carbon nanotubes nor the highest current density that’s been achieved. In 2013, a team based at IBM’s Thomas J. Watson Research Center, in Yorktown Heights, N.Y., reported that a suspension of carbon nanotubes in oil could be used to produce more than 500 carbon nanotubes per micrometer and similar current densities.

But in the IBM experiment there were metallic carbon nanotubes in the mix, which conduct current even when a transistor is supposed to be off. This may have contributed to a fairly low ratio of on-current to off-current, which, in the shortest IBM transistors, maxed out at around 600:1, Shulaker estimates. The Stanford team’s ratio is around 6,000, an indicator that only a small amount of current is leaking through the devices when they’re supposed to be off. (Designers typically aim for an on/off ratio of about 10,000 for the CMOS devices used in smartphone and computer processors.)

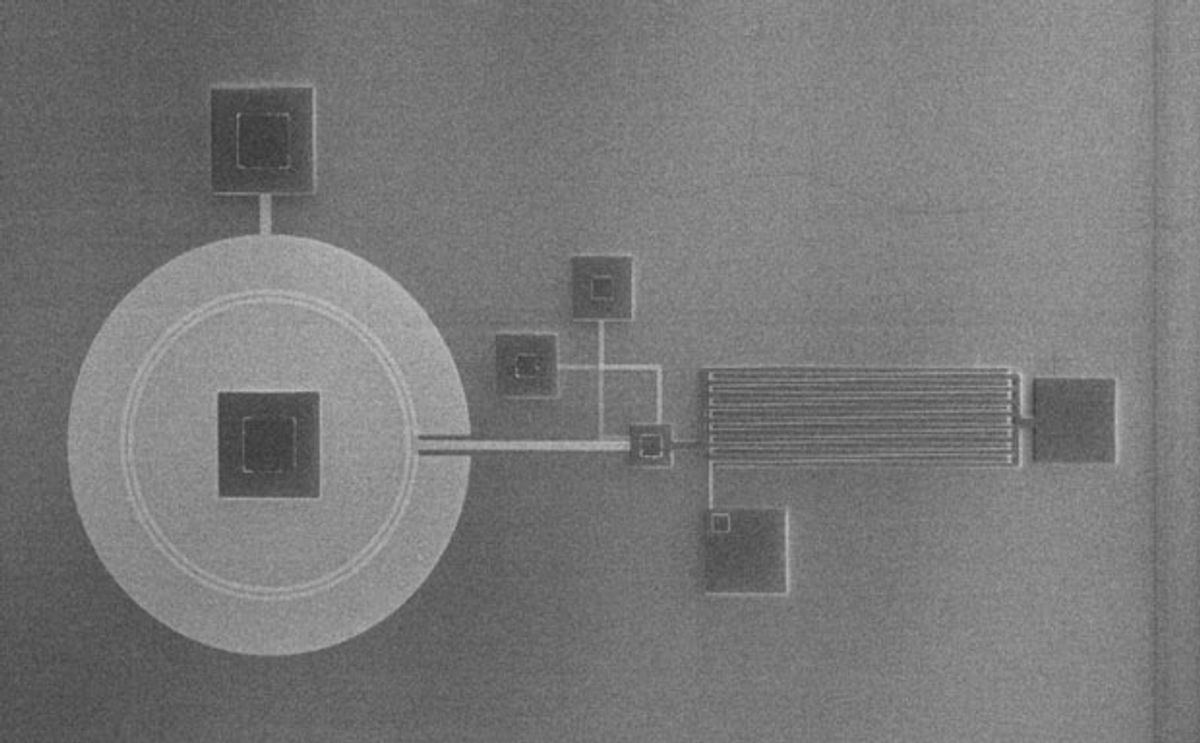

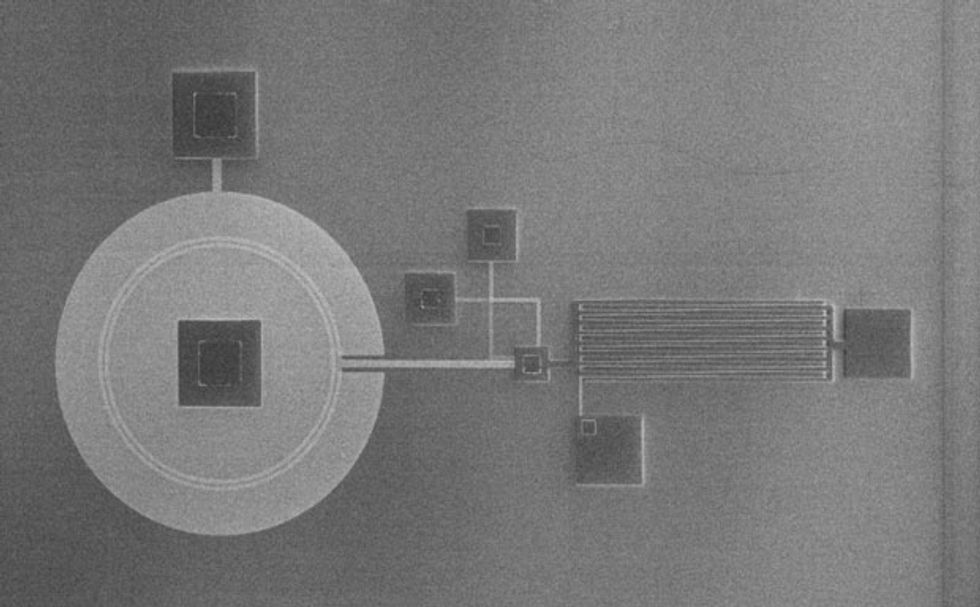

To prove the approach’s compatibility with silicon, the Stanford team used the multiple-transfer strategy to create a “monolithic” 3-D integrated circuit. A monolithic IC is made in one fell swoop on a single silicon substrate by building layers of devices one on top of the other, with dense metal wiring connecting them.

The team built a crossbar switch—a circuit that can be used to connect different inputs and outputs—out of a layer of silicon, two layers of resistive RAM, and then a layer of carbon nanotube transistors. They were able to build the stack of circuits without raising temperatures above 400 °C, which could damage the transistors.

“These guys are masters of stacking,” says Sung Kyu Lim, who works on monolithic 3-D design at Georgia Tech. Although researchers at CEA-Leti, in France, have stacked logic on top of logic, Lim says this is the first demonstration he’s seen of memory and logic stacked together in a monolithic fashion: “They’re the first one demonstrating that this is possible,” he says. The combination of logic and memory could dramatically reduce the time and energy needed to move information inside a computer.

But bringing carbon nanotube ICs into mass production could still be a ways off, Lim notes. The current-carrying channels in the Stanford team’s carbon nanotube transistors are 400 nanometers long, about 10 times the size of state-of-the-art devices. “You want the devices to be smaller and the circuits to be larger,” Lim says.

The next step is indeed building speedier circuits with shorter-channel transistors, Wong says. And it should be possible; previous work at IBM has shown carbon nanotube transistors with channel lengths smaller than 10 nm. But Wong says there are hurdles that must still be overcome on the road to high-performance circuits. First on his list are the metal contacts that connect to the nanotubes, which, like the contacts in other devices, balloon in resistance as they get smaller. Still, he has high hopes: “Having a technology that can compete with silicon in an academic setting would be tremendously exciting.”

This article originally appeared in print as “Carbon Nanotubes, Stuffed and Stacked.”

Rachel Courtland, an unabashed astronomy aficionado, is a former senior associate editor at Spectrum. She now works in the editorial department at Nature. At Spectrum, she wrote about a variety of engineering efforts, including the quest for energy-producing fusion at the National Ignition Facility and the hunt for dark matter using an ultraquiet radio receiver. In 2014, she received a Neal Award for her feature on shrinking transistors and how the semiconductor industry talks about the challenge.