Winner: The Ultimate Dielectric Is...Nothing

IBM packs wires in vacuum to speed chips and save power

The running joke at IBM’s site in East Fishkill, N.Y., is that engineers who have been working there for 30 years still have trouble locating their own offices. And sure enough, finding your way through the low hedge of cubicles in the 300 Building is very nearly impossible. That’s because the architect designed it to reproduce the tortuous wiring scheme inside a microprocessor. That’s the rumor, anyway.

Now imagine having to insulate such a tangle, but in microcosm: many kilometers of nanometer-scale copper conductors in a sliver of semiconductor the size of a child’s thumbnail. That was the challenge facing IBM Fellow Dan Edelstein, who 10 years ago led an industry-wide switch from aluminum to copper chip wiring that has enabled every microprocessor since 1998. Now Edelstein is hatching his next revolution. With his colleague Satya Nitta, he is surrounding the conductors in IBM’s bleeding-edge microprocessors with holes. He thinks his competitors will have little choice but to follow his lead in the infinitesimal realms he is staking out.

Those holes—IBM calls them air gaps—are actually cavities of vacuum embedded in the insulation that surrounds the chips’ wiring. Air gaps may well be the solution to a problem that has been tripping up chip manufacturers for almost a decade: when you cram nearly 10 kilometers of wiring into a space smaller than a postage stamp, the signal on one wire is felt by its neighbors. The electric field between them can then impede the flow of current through the wires, and that slows down the signals they carry.

IBM is a bit cagey about saying exactly when the new technique will go into production, other than that it will be in chips slated for production in 2009. Sources familiar with the technology, however, say there’s a chance that it might go into production sometime this year.

The advance, like so many in the industry, comes not a minute too soon to prop up Moore’s Law, which insists that transistor density will double about every 20 months. That’s how Intel got from its 33-megahertz 486 processor in 1989 to its 2.9-gigahertz Xeon processor in 2007.

Ever since the microchip was invented, the basic rule of thumb has been that transistor size is the limiting factor on chip speed. “Transistors are the fluke of nature,” Edelstein explains. “They get faster when they get smaller, but nothing else does.” A microprocessor may have hundreds of millions of transistors, but no matter how fast those transistors get, they depend on wires, which get much slower when they get smaller. That’s a problem for the transistors, which must compensate by using more power. It’s also a problem for the wires, which must radiate heat from the extra power the transistors are using.

As it turns out, the source of the signal lag is not so much the metal interconnects themselves but rather the insulation between the wires. So the question of the moment is, what can you put between those wires to prevent the signal from leaking?

Vacuum is the best insulator known. Since the 1990s, many chip manufacturers besides IBM, including Infineon Technologies, in Munich, and STMicroelectronics, in Geneva, have experimented with vacuum cavities, and some have even built prototype chips. But two problems have kept the technology from entering production. A chip needs insulation to shield its wires from one another, but it also depends on that insulation for structural support to survive what can be a rough manufacturing process, as well as the often high temperatures on a printed circuit board. Fill the insulation with holes, and the whole chip might collapse. The second problem is making air gaps compatible with standard chip-fabrication techniques. Despite the performance gains that companies have realized on their test chips with air gaps, added equipment and exotic materials have canceled out the performance gain with a money drain.

But the state-of-the-art chip IBM unveiled back in May could usher in the era of vacuum. “The technology is quite impressive and innovative,” says James Meindl, a director of the Microelectronics Research Center at Georgia Tech. It’s structurally sound, and IBM’s design has reduced the signal lag enough to “buy back” between 10 and 15 percent of chip speed that would otherwise be lost. That performance boost is about what you get from doubling the density of a chip’s transistors, and IBM did it without exotic materials, new tools, or costly redesigns. “It’s a very straightforward process,” says James Watkins, codirector of the MassNanoTech Institute at the University of Massachusetts in Amherst. “It stands a good chance of being mainstreamed.”

The industry has been insulating microchip conductors with silicon dioxide (glass, basically) since the first commercial integrated circuits were introduced in 1961. For years, the wires that carry the electrical current on a chip were barely an afterthought. “The transistor was everything,” says Edelstein.

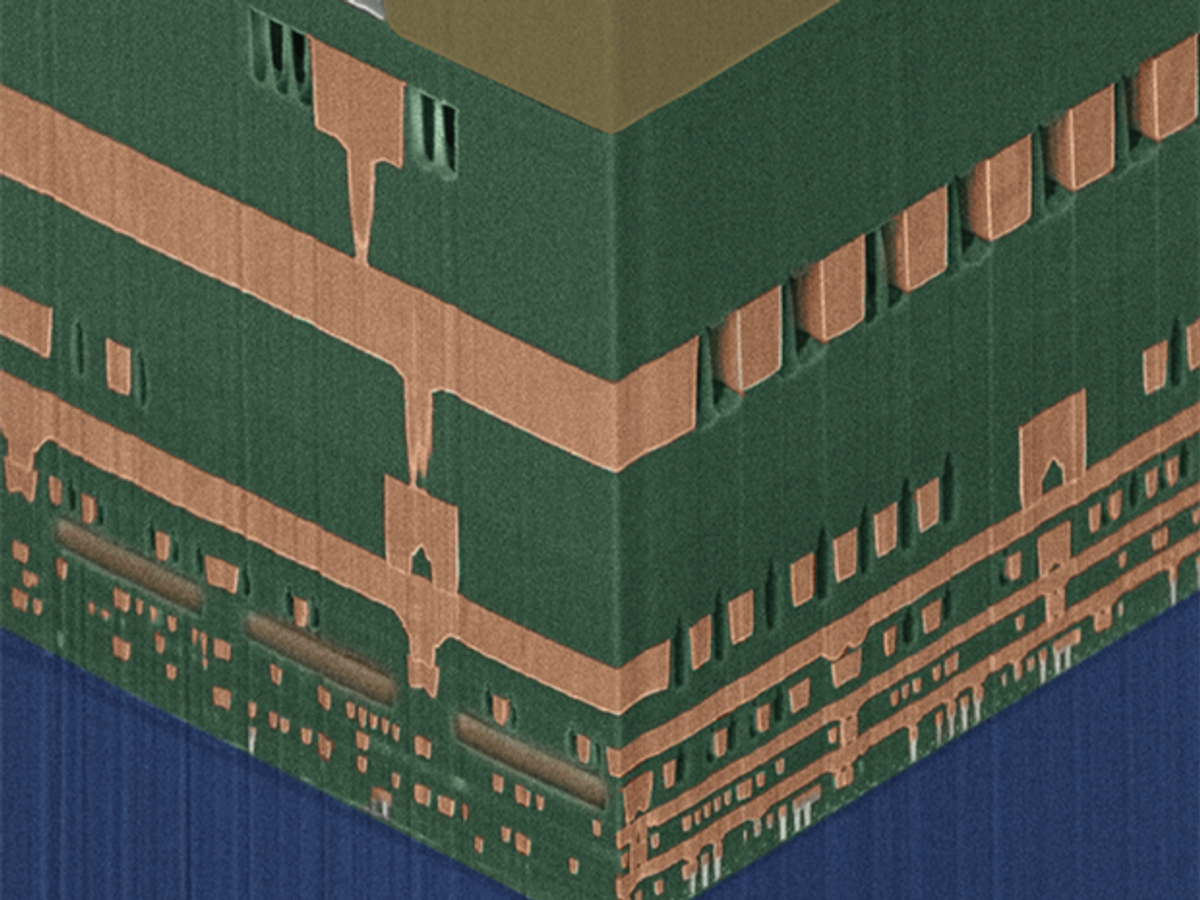

But by 2000, joining the millions of transistors into a functioning integrated circuit necessitated nearly 2 km of wire. Nobody wants wider chips (space on a circuit board is always tight), so the only way to pack in all that wiring is to make them taller. To do that, individual wiring levels—each consisting of the glasslike insulating material inlaid with a network of the copper wiring—are stacked on top of each other by a process called dual damascene, named for the ancient Middle Eastern method of inlaying gold or silver into a sword.

To build the stack, the base level—the dinner-plate-size wafer containing the transistors—is first covered with a layer of insulation made of an impure glass variant. A pattern is transferred onto it by photolithography, which is similar to photography: the insulation is covered with a light-sensitive material called a photoresist, onto which a pattern is projected, using ultraviolet light streaming through a mask. When the light hits the exposed areas of the photoresist, it changes the material’s chemical properties: the area in the mask’s shadow remains strong and corrosion resistant, but the area exposed to light has become vulnerable. A corrosive plasma eats away the vulnerable areas and the insulation beneath, creating a network of trenches.

Now this level is ready for its wiring. First, the glass is lined with a thin, corrosion-resistant film. Then the trenches are filled with copper. The wafer is scoured and polished to a flat surface, until the only metal that remains is inside the trenches. The result is a glassy surface inlaid with many meters of glittering copper canals.

The last step is the application of a capping layer of organosilicate—silicon dioxide that has been impregnated with carbon. This layer separates the levels from each other and provides added structural support. Then the process starts anew. Today’s state-of-the-art chips can have up to 10 of these levels. But they are not strictly identical. Instead, they gradually increase in thickness, so that the lowest level of wiring is smaller and more delicate than the topmost level by a factor of eight. At the higher levels of the chip, the insulation is thicker and the wiring more substantial.

But this process no longer suffices. There’s too much drag on the signal traveling down the tiny wires. The culprits are capacitance and resistance. Long, thin wires have more resistance, of course, than short, thick ones. So you can’t do much worse than a nanoscopically thin collection of wire segments that would span a small town if laid end to end. Think of trying to suck a drink through a 2-meter-long cocktail straw. This is why the industry abandoned aluminum for copper wiring—its greater conductivity overcame the resistance of thin wiring.

The other—and bigger—problem is capacitance. When wires are cramped so closely together, the electric field from one wire is felt by neighboring wires, and that creates an unintended capacitor. A capacitor stores electrons, somewhat like a battery. Storing electrons is great for batteries, but it’s bad when those electrons need to get somewhere else. Picture the electrons traveling down the wires in waves. The capacitance in the wire acts like a breaker, damping the waves’ motion and therefore slowing the rate at which the signal can travel from one end of the wire to the other.

A transistor on a digital chip is just a switch that operates at incredibly high speed—2.7 billion times a second in the current generation of microchips. The higher the capacitance between the wires, the more power the transistor needs to operate at that speed. The result is power drain. Reducing capacitance lets the chip use less power to switch at the same speed.

Making the wires thicker isn’t an option, so the only solution is to improve the insulator’s dielectric constant, a measure of the insulation’s ability to concentrate an electric field. The dielectric constant is usually referred to simply as k. The lower the k-value, the better the insulation.

The lowest possible k-value is 1.0, and the only way to achieve that number is with the ideal insulator: vacuum. Natural glass has a k-value of 4.2. When that started to become a problem, researchers began pushing that number lower by “doping” their silicon dioxide—mixing the glass with other elements, like fluorine and carbon. For decades, chip manufacturers have been groaning under the strain of pushing the dielectric constant from 4 to the mid-3s (fluorinated silicon dioxide) to the high 2s (silicon dioxide with severe carbon doping). The problem is that loading the insulator with carbon also changes its density, making the material softer and weaker. Insulation will tolerate only so much doping.

By figuring out how to use vacuum, IBM shot the industry-leading dielectric constant from a spongy 2.7 to an eyebrow-raising 1.9. The resulting microprocessor leapfrogs a full generation in total chip performance without a chip redesign.

So how do you make bubbles full of nothing? There are two ways to make air gaps, and how IBM makes them depends on where in the chip the gaps need to go. For higher levels, the spacing between the wires is less critical, so the vacuum pockets can be carved conventionally—with masks, ultraviolet light, and plasma. As usual, after the interconnect pattern is projected onto the insulation, plasma digs out the channels, and the wiring is laid. That process is then repeated to carve holes into the insulation around the wiring. The level is capped off with organosilicate in a vacuum chamber and, voilà, air gaps. The organosilicate cap layer remains, holding the wiring in place at the top and bottom, but the carved-out spaces between the wires are empty.

This strategy doesn’t work at the lower levels, because the tiny spaces between the wiring don’t tolerate the slightest error. At the lowest levels of the next-generation chips, the width of the insulation between wires is about 50 nanometers. Not even the best production processes can create holes inside features that small without nicking the wiring. Thus exposed, the copper would melt under the extreme heat of the plasma and leak through the air gap, fuse with neighboring wires, and ruin the chip. Conventional techniques simply can’t ensure enough precision. Edelstein and Nitta had to invent a different way to make the really, really tiny holes.

They turned to organic chemistry, and their own version of something called a block copolymer. A polymer is a long chainlike molecule, and in a block copolymer, the links of the chain are repeating blocks of two different chemicals. Imagine a string of Christmas tree lights that, instead of being randomly distributed, are grouped so that a bunch of red bulbs is followed by a bunch of green bulbs, which is followed by a bunch of red bulbs, and so on. SBS rubber, used in shoe soles and tire treads, is such a substance.

But IBM’s block copolymer assembles itself. The molecules’ intrinsic chemical properties cause them, upon exposure to heat, to assemble into a two-dimensional mesh of regularly spaced 20-nm cylindrical holes. Think of a sieve. The resulting substance teems with trillions of these holes—much smaller than anything you can make with light and plasma. With the chip prototype IBM demonstrated in May, Big Blue was the first to take self-assembly technology out of the lab and into the semiconductor fab.

“The polymer is easy to use and inexpensive,” says Charles Black, a researcher at Brookhaven National Laboratory, in Upton, N.Y., who developed the technology while at IBM. But the extra processing steps amount to a cost increase of about 1 percent per layer, and that will mean different things to different customers. “A high-end, mission-critical system will want these in maybe four of its layers,” Edelstein says. “But for a cheap chip in a video game, you want to keep costs down.” That’s why the step is an optional part of an otherwise normal manufacturing process.

The process starts the usual way, with channels of interconnect embedded into a layer of glasslike insulation and capped off. But that silicon dioxide cap is then subjected to additional steps.

First, the liquid copolymer is applied. Heat causes it to assemble itself into the 2-D 20-nm “sieve” template. Ions bombard the surface, extruding those 2-D holes into long tunnels that puncture the insulation beneath, creating trillions of tiny 3-D columns.

Next, the whole thing is flushed with an acid that eats the walls between the 20-nm-wide tunnels, leaving clean cavities. The copper is unscathed because the acid attacks the insulation preferentially. The cap layer under the copper is also unscathed because the 3-D tunnels pierce only the insulation between the wires. The final step—the application of the next cap layer—leaves the perforated level sandwiched between two unbroken sheets of glass holding the copper wiring between them firmly in place. Since this all takes place inside a vacuum chamber, the sealed-off cavities retain a vacuum. The process is repeated for levels two, three, and four, until conventional methods can be used again.

The chip industry has spent years pursuing the right way to make air gaps. Though myriad ways to make air gaps exist on paper, Nitta says, most of those techniques are not realistically manufactured. “That’s why our results are so much more significant,” he says. “We put the chip in IBM’s server, and it booted up. We even got chip performance data.”

IBM’s closest rival in this technology is STMicroelectronics, which has been working with air gaps for 10 years. However, ST’s method works only in the high, bulky levels of interconnect.

The most common mistake, Nitta says, is using insulation made from special materials, which increases the cost and complicates the manufacturing process. Intel, for example, uses what it calls nanopore technology, in which an insulating material populated with tiny, 2-nm spherical pores approximates the benefits of vacuum. Michael C. Mayberry, director of components research at Intel, says that unlike IBM’s process, nanopore technology requires no extra steps. He predicts that performance gains “will be perhaps 15 percent.” That number is comparable to IBM’s result, but Mayberry is skeptical of IBM’s projections. “Many of the wild claims I’ve seen reported don’t materialize,” he says. To date, Intel has not demonstrated its vacuum-approximating technology on any working chips.

Not everyone thinks the extra manufacturing cost is worth the performance boost. “A 15 percent improvement does not seem that exciting,” says STMicroelectronics interconnect expert Davide Pandini. He speculates that the new technology’s margin of error might substantially drive down the performance gain.

Mayberry says Intel is deliberately moving away from research into air gaps because of questions about structural integrity. Some critics have seized on the concern that IBM’s pocked chips won’t be as physically strong as those with solid insulation.

But Edelstein and Nitta argue that their chip has been put through its paces. The air gaps are not ubiquitous. “We only put them in the critical places where they do the most good,” says Nitta. The proof is in the chip’s effective dielectric constant, which is not the 1.0 of pure vacuum, but rather 1.9. “We had to make the chips tough enough to survive ship shock,” Nitta says. Ship shock is a way of torture testing a chip by simulating a trip from scorching Arizona to frigid Alaska. Nitta says the chips have survived 1000 such cycles without damage.

IBM is making the technology available for license by its research partners, including AMD, Freescale, Sony, and Toshiba. AMD’s John Pellerin says the company is considering IBM’s air-gap technology to fabricate microprocessors of the next generation, known as the 32-nm node, which is expected to debut in 2009 or 2010.

The air-gap technology is now undergoing testing on three generations of chips—the current 65-nm generation, 45 nm (which makes its debut for IBM later this year), and 32 nm. Officially, IBM is adamant that the technology will not be used before 2009. But industry analysts speculate that the company will spend the coming year trying to push the technology into the 45-nm chips.

Regardless of which generation of chips is outfitted with air gaps, Edelstein predicts that the technology will be as transformative as copper wiring was a decade ago.

IBM’s Air-Gap Technology

Winner: Semiconductors

Goal: To find a way to use vacuum to insulate microchip wiring.

Why It’s a Winner: Other companies have been trying for years, but IBM made it work.

Players: IBM

Where: East Fishkill, N.Y.

Staff: 8, working for 4 years

Budget: Info not available