Researchers at the Moscow Institute of Physics and Technology (MIPT) have proposed a new tunnel transistor based on bilayer graphene that could reduce its power consumption, allowing a significant increase in processors’ clock speeds. In their simulations, the MIPT researchers calculated that the clock speed could be increased by as much as two orders of magnitude.

“The point is not so much about saving electricity—we have plenty of electrical energy,” said Dmitry Svintsov of MIPT in a press release. “At a lower power, electronic components heat up less, and that means that they are able to operate at a higher clock speed—not one gigahertz, but ten for example, or even one hundred.”

Tunneling transistors have become an increasingly attractive alternative to traditional transistors that operate on the basis of electronic barriers that block electrons from passing through. The problem with traditional transistors has been that as chips have continued to shrink, the barriers have gotten thinner and the electrons just pass right through. The tunnel transistor flips the scheme on its head, offering a kind of “if you can’t beat them join them” solution in which you want the electrons to tunnel through the barrier.

Tunnel transistors operate by always keeping the energy barrier up rather than raising or lowering it to control the flow of current. By taking advantage of a quantum effect, the device switches on and off by altering the likelihood that electrons on one side of that barrier will materialize on the other side.

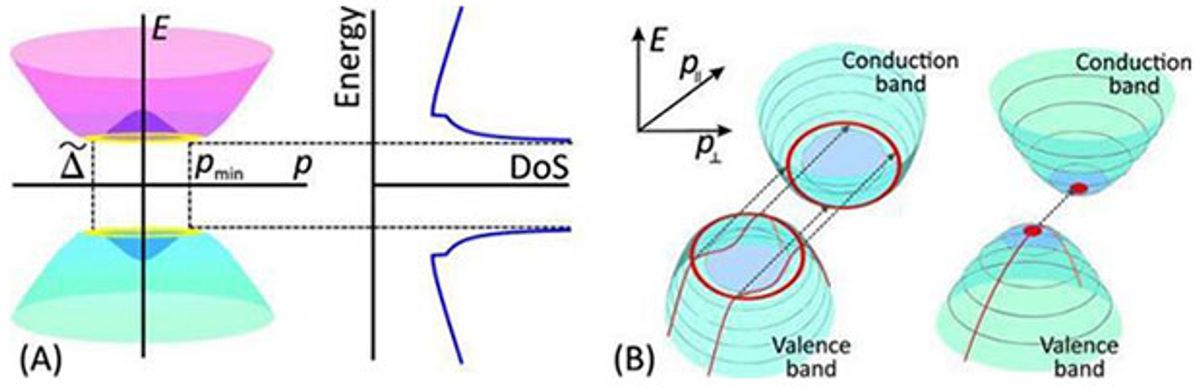

In research described in the journal Scientific Reports, the MIPT researchers developed a computer model of just such a tunnel transistor fabricated from bilayer graphene. Bilayer graphene was used because its valence and conduction bands take on the shape of a “Mexican hat” as opposed to most semiconductors in which the bands take on a parabolic shape.

What the modeling revealed was the number of electrons that can occupy spaces close to the edges of the “Mexican hat” tends towards the infinite. When a small voltage is applied to the gate of a transistor, an enormous number of electrons at the edges of the “Mexican hat” begin to tunnel at the same time. The result of this sudden mass tunneling is a sharp change in current, despite only a small voltage having been applied. It is this high performance at such low voltage that accounts for the low power consumption.

“The next step in the research will be the fabrication of the FET prototype, measurement of the FET characteristics, and its comparison with the modeling,” Svintsov told IEEE Spectrum in an e-mail interview. “As the next step in theory, we shall continue the search for materials where the peculiarities of carrier spectrum allow for the abrupt switching of tunnel current.”

After they fabricate their FET prototype, there are a few engineering issues that would then need to be addressed before such a transistor could be mass produced.

Svinstov says that an approach to growing the graphene bilayer directly on boron nitride substrates would need to be used and that sub-10-nanometer gaps between metal gates would need to be fabricated. Both of these have already been performed in labs, according to Svinstov.

Dexter Johnson is a contributing editor at IEEE Spectrum, with a focus on nanotechnology.