People often think that Moore’s Law is all about making smaller and smaller transistors. But these days, a lot of the difficulty is squeezing in the tangle of interconnects needed to get signals and power to them. Those smaller, more dense interconnects are more resistive, leading to a potential waste of power. At the IEEE International Electron Devices Meeting in December, Arm engineers presented a processor design that demonstrates a way to reduce the density of interconnects and deliver power to chips with less waste.

“If you supply one volt at the power regulator, most likely you don’t get one volt at the transistor,” explained Divya Prasad, a senior research engineer at Arm. A 10 percent voltage margin between the regulator and the transistors it’s meant to power is considered acceptable. However, “it’s getting harder and harder to meet this.”

Prasad and her colleagues implemented a Cortex A53 CPU design using a future 3-nanometer process developed by Belgian research firm imec. The world’s largest foundry, TSMC, is on track to reach full 5-nanometer production in 2020, so 3-nanometers is only a short way off.

They made three variations on the design. One dealt with the problem of power delivery in the same manner as is done today, where circuits access power from the network of interconnects above the transistors. Another used what imec calls buried power rails. Here, rails of ruthenium were built into the space below the silicon surface, these were energized by vertical connections to the network above and then tapped at regular intervals to provide power to circuits.

Earlier this year, imec engineers showed advantages for SRAM cells using buried power lines. SRAM, typically a 6-transistor circuit, is particularly sensitive to interconnect resistance, which can slow read and write performance. In simulations, buried ruthenium power rails led to 31 percent faster reads and 340-millivolt lower write voltages.

The final variation had buried power rails that were instead energized by micrometer-scale vias that ran vertically through the backside of the silicon.

Using the ordinary approach, the Arm engineers were unable to meet the 10 percent voltage margin, because too much power was lost in the interconnect network’s resistance, Prasad explained. With buried power rails and frontside power delivery, the design was able to hit the margin, but the engineers had to trade performance for power loss.

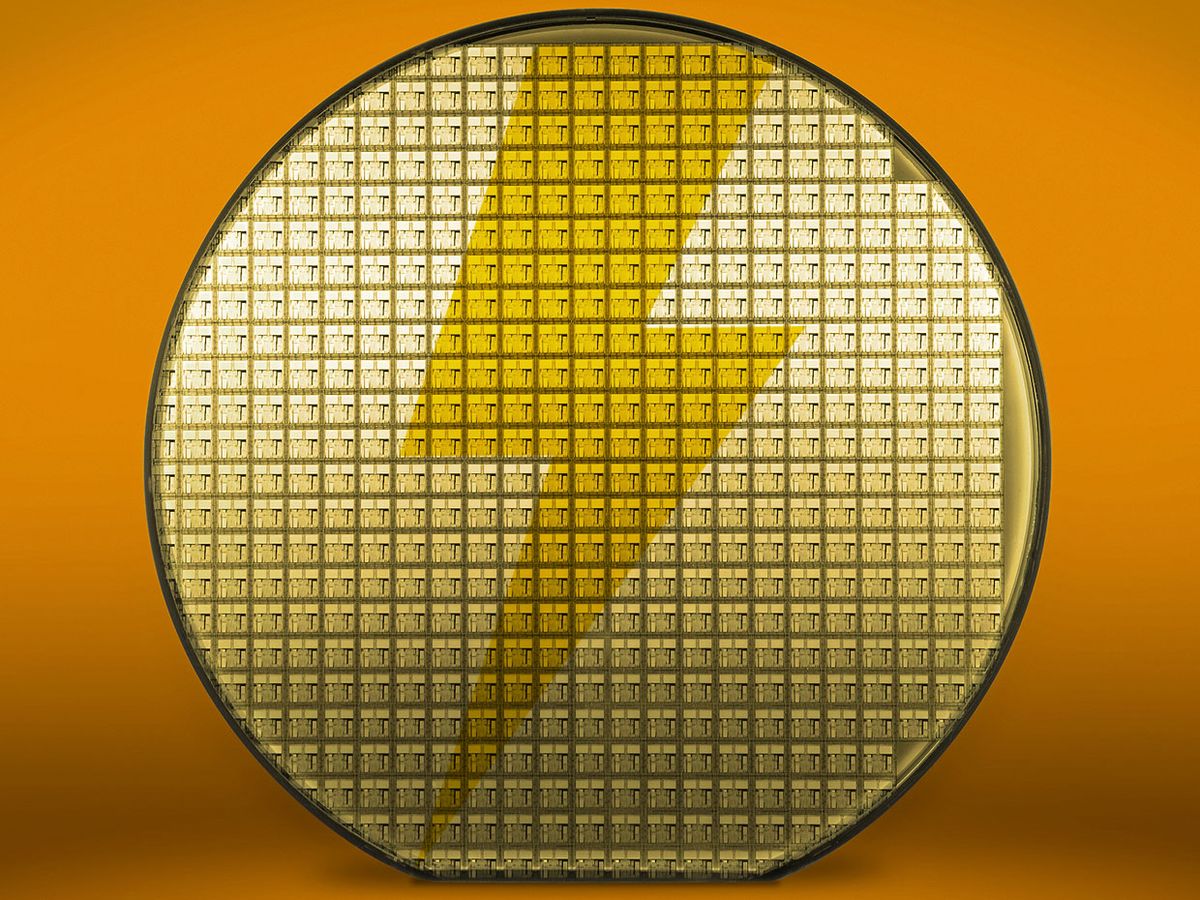

Buried power rails with backside delivery was the clear winner, meeting the margin and dropping only 1 percent of the voltage without harming performance. The only trade-off is the complexity of manufacturing the backside network, Prasad noted. To make it, the frontside of the wafer must be fully processed, including the construction of the buried power rails. The wafer is then flipped over, and the silicon is removed down to a mere 500 nanometers thickness. Then vertical connections less than 1 micrometer across, called micro-through-silicon vias (microTSVs), were built to contact the buried power rails. A simple network of interconnects on the backside links the microTSVs into a power delivery network.

“We’re pretty excited about backside power delivery,” said Prasad. In the best case scenario, it provided seven-fold improvement in voltage loss over the other two options.

Samuel K. Moore is the senior editor at IEEE Spectrum in charge of semiconductors coverage. An IEEE member, he has a bachelor's degree in biomedical engineering from Brown University and a master's degree in journalism from New York University.