Future Fab

How software is helping Intel go nano—and beyond

The modern microprocessor is one of the premier markers of technological achievement. And rightly so. But if a billion transistors on a postage-stamp-size chip impress you, consider the fabrication facilities that put them there. And not just on one chip, but on hundreds of them on dinner-plate-size wafers, which move by the thousands through the manufacturing line 24 hours a day, 365 days a year.

In a single day, a state-of-the-art fab can make nearly 100 trillion transistors, roughly 250 times the number of stars in the Milky Way galaxy. Such facilities are by any standard the most complex, and, at an average cost of US $3 billion to build and equip, the most costly factories ever built by humankind.

Their sheer scale astounds—one of Intel’s current-generation semiconductor fabs scatters nearly a thousand multimillion-dollar machines in an area more than twice the size of a regulation soccer field. These machines perform more than 500 different steps to make a chip, and they do it around the clock. That adds up to a mind-boggling 10 million processing steps in each fab every week.

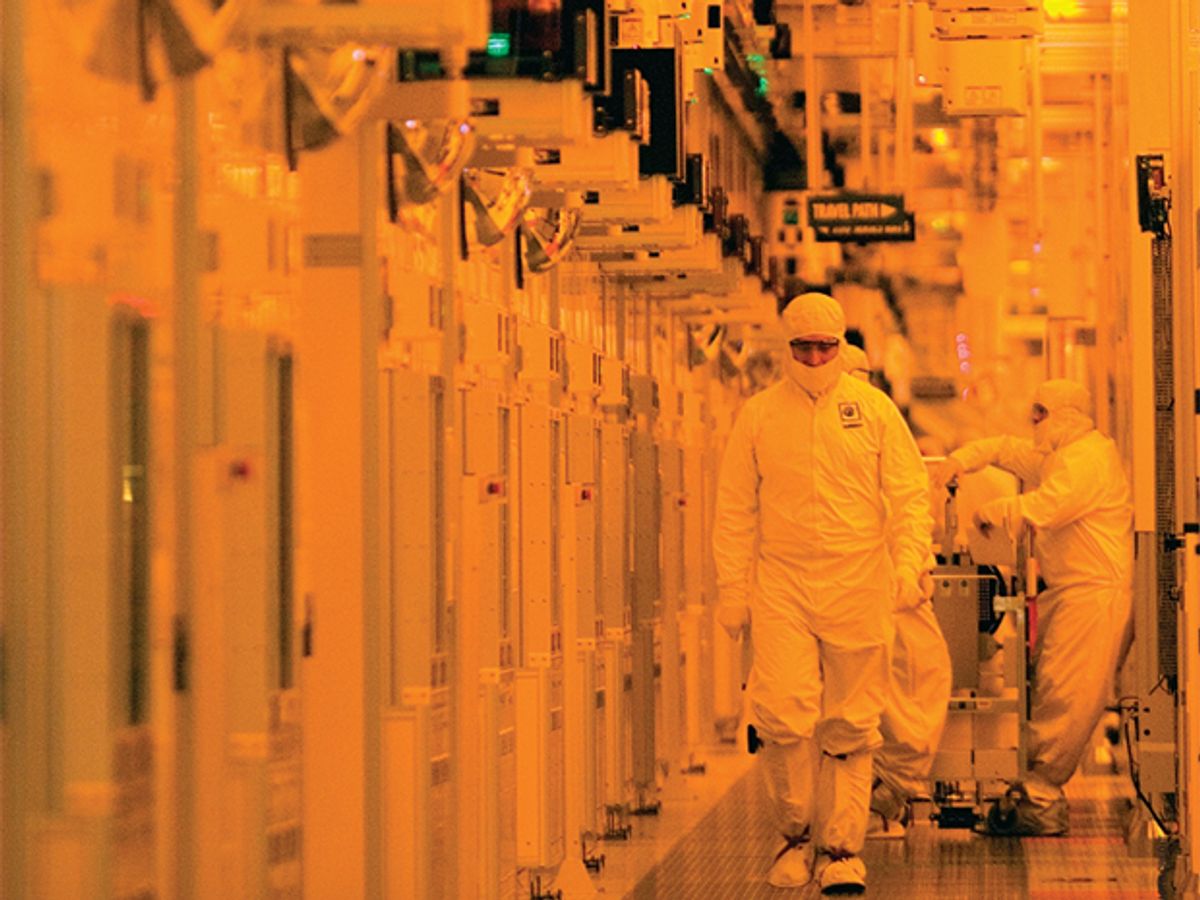

If you think that’s too much for mere human beings to handle, you’re right. Increasingly, it’s software, rather than bunny-suited people, that produces chips. In fact, our ability at Intel to beat our competitors to market with new technology depends enormously on the software we use to test, adjust, and perfect the manufacturing processes in our fabs.

Today’s state-of-the-art fabs produce chips on 300-millimeter-diameter wafers [see “Special Delivery”]. By our count, there are 43 commercial 300-mm fabs in production as this issue goes to press, with perhaps a dozen more slated to come online by year-end. Some are more automated than others, but most 300-mm fabs have at least a material-handling system that uses software-controlled robots and monorails to transport wafers to the myriad tools needed to make chips—etching chambers, wafer polishers, photolithographic steppers, and the like. Most IC makers also buy or write manufacturing software that tracks wafers through the fab, scheduling software that sends wafers to the right tools at the right time, and process-control systems to manage the chip-making recipes—the mix of gases, chemicals, metals, and semiconductors that constitute each chip.

The software suite that we write and manage, dubbed Automated Manufacturing Technology, or AMT, monitors and controls the hundreds of steps wafers must pass through on their way to becoming Pentium, Itanium, and Core 2 Duo processors, as well as other high-end Intel microprocessors. This software makes it possible to run a 300-mm factory with far fewer people than we needed to run our older 200-mm fabs. These days people venture out onto the fab floor only to attend to machines that the software system has sensed need repairs or routine maintenance.

AMT also plays a crucial role in Intel’s multibillion-dollar-a-year R&D operations. Researchers use the technology development manufacturing line installed in our fab in Hillsboro, Ore., to create and hone the manufacturing processes for all of Intel’s fabs. The procedures and recipes we concoct there for next-generation chips will be copied exactly at one or more of the company’s five (soon seven) 300-mm fabs. That development line takes advantage of the same hardware and software capabilities as the manufacturing lines that are producing Pentium and Core 2 Duo and Quad processors alongside it in our Hillsboro fab. This line also tests out new machines and software routines that are being specifically developed and tuned for future generations of chips.

This close coupling of our development operations and manufacturing allows us to stay on the approximate two-year cycle defined by Moore’s Law. The current-generation process, which we launched in 2005, produces chips in which the minimum half-pitch—half the distance, center to center—between two wires can be as small as 65 nanometers. By the end of 2006, we had already shipped 70 million microprocessors produced by our 65-nm process. In January of this year, we completed the development of the next generation of chip-making technology, which by the second half of this year will be knocking out chips in the 45-nm process. We are also well into developing 32-nm processes, to be unveiled in 2009.

Before we discuss the software that runs our R&D line and fabs, here are the basics of the chip-making process it controls.

A wafer begins its trip through the fab as a mirror-polished disk of 99.9999999 percent pure silicon, 300 mm in diameter and not quite a millimeter thick. The wafer then passes through the first of many patterning processes to create the chip’s astounding profusion of transistors [see “Hands Off”]. These patterning processes, known as photolithography, are the heart of chip making and they are carried out repeatedly, up to 30 to 40 times for an advanced chip like a 64-bit Itanium microprocessor.

Each time a wafer goes through one of these photolithography cycles, a liquid polymer called a photoresist is applied to it. Then it goes into a step-and-repeat projection camera, better known as a “stepper,” which exposes a pattern onto the resist-coated wafer. For each exposure, the stepper moves to a new position, each one corresponding to a single chip.

The pattern is projected onto the wafer in ultraviolet light through a photomask, a thin plate of transparent quartz covered with the pattern defined in chrome of a particular chip layer. After the wafer has been exposed, it is washed with a solvent, removing the undesired resist and leaving the image of the photomask on the wafer.

Each time the wafer is patterned, one of three different processes is performed. In some cases, the wafer will be etched to remove material. This can involve a liquid acid or a high-temperature plasma, both of which will eat away any surface not covered by the resist. During other steps, the wafer is put through another diffusion or deposition process that adds material to it. In this case, the resist acts as a barrier, preventing the new material from adhering to parts of the wafer.

The third process involves changing the concentration of ions in parts of the wafer to adjust the conductivity of the semiconductor. Here the resist again acts as a barrier, preventing the ions from penetrating into the protected parts of the wafer. After the wafer has been processed, all the remaining resist is removed with a special solvent.

This process is repeated many times to create all the components of a transistor. Then, the process is repeated several more times, adding layers of metal interconnects to the components to create functional circuits. Afterward, insulating material is added to the wafer, the wafer is patterned for interconnects, metal is deposited and polished smooth, and the next layer of insulation is added.

While the basic chip-making processes have been around since the early days of semiconductor manufacturing, more than 35 years ago, several significant changes have occurred. For instance, there are a lot more photolithography cycles today to create the layers of wires needed to connect the proliferation of transistors mandated by Moore’s Law.

Also, shorter wavelengths of light are used to resolve smaller features, new materials are always being introduced, new processes such as plasma etching and silicon straining have come into vogue, and optical tricks of remarkable complexity are employed to produce features even smaller than the wavelengths that are resolving them.

And, last but not least, the whole process is now controlled by software.

The AMT suitehas four major components: the Manufacturing Execution System, the Process Control Automation Framework, the Engineering Analysis Framework, and the Material Handling and Tool Control. Each is composed of several programs, and each of those programs controls a different part of the chip-making process.

One program in the Manufacturing Execution System that’s called Fab-Wide Scheduling, for example, acts like the world’s most sophisticated traffic cop: it tracks all the wafers through the fab to ensure that they pass in and out of different machines in sync with all the other wafers that are simultaneously moving from machine to machine. Another program, in the Process Control Automation Framework called Advanced Process Control, automatically detects random variations in the processing equipment—maybe a chemical vapor deposition machine has deposited too much metal to make a wire, for instance—and adjusts the recipe accordingly.

On each manufacturing line, as well as on the main technology development line where we refine recipes for new chips, the AMT system takes thousands of readings from hundreds of machines. There are defect-density and film-thickness readings from quality inspection tools, temperature and pressure readings from deposition and etch tools, and even readings of the velocity of the gas flowing to diffusion furnaces. All this information feeds into the fab’s database, which typically contains tens of trillions of bytes of data, or five to 10 times the amount of information you’d find in the entire print collection of the U.S. Library of Congress. These data are crucial to determining the merits of the different recipes our researchers experiment with while creating a new chip. Automated engineering programs, part of the Engineering Analysis Framework, evaluate transistor performance, wafer yields, and manufacturing processes related to the chip-making experiments run on the technology development line. These proprietary programs identify recipes that improve transistor performance and the yield of chips, reduce power consumption and heat dissipation, and otherwise help produce better chips faster. This automated analysis of hundreds of thousands of data points enables fast tuning of the manufacturing recipes in the fab.

How fast can these recipes be put into use? In the blink of an eye, basically. Once we determine that a new recipe works for, say, an etching bath, the system feeds it back to the chip-making tools on the technology development line and starts using it right away. So a batch of wafers that is already in the midst of photolithography can benefit immediately from these revised instructions.

For example, suppose a wafer lot has just been exposed in a stepper and is awaiting a cleansing chemical bath in an etcher. By the time it gets to that etching bath, there might be a better recipe awaiting the wafers than the one used for the batch that just exited the machine. These experiments continue until the microprocessor recipe is fine-tuned for use in all the company’s high-volume manufacturing lines.

The AMT suite of programs has improved tremendously over the last couple of decades. The most recent innovation, developed by Intel’s Logic Technology Development group, is a piece of software we call “the grid.” It allows all our machines and the dozens of applications that make up the AMT suite to communicate with each other to fully automate fab operations. The grid is basically a giant electronic bulletin board, where machines and wafers inside the fab announce their respective states and locations.

The AMT programs—written in a variety of programming languages, including C, C++, and C#—all speak a common language: eXtensible Markup Language, or XML. Each program posts messages encoded in XML on the grid for other programs to see and, if necessary, act upon. The chip-making tools also post messages on the grid in XML. Each tool has its own control program, which, among other things, translates the tool’s message from machine language into XML.

To see how the grid improves the manufacturing flow and the R&D process, let’s look at a 25-piece lot of experimental wafers—call it Lot X500. The wafers, coated with resist, are about to go into the stepper, where the mask patterns will be repeatedly projected onto them. There are dozens of steppers in each of our fabs. We’ll call this one Stepper No. 8.

First, the Manufacturing Execution System (MES) choreographs all the steps necessary to get Lot X500 through the next manufacturing step before anything is physically moved. The MES knows everything about the tens of thousands of wafers in the fab and all the machines that process them—how many steps each wafer has gone through and its location in the fab, for instance, or the health of each machine and whether or not it is busy.

The MES knows, for example, that Lot X500 has already passed through several process steps and is sitting in a front-opening unified pod, which is basically a kind of storage and transport container for batches of wafers. This pod is in a larger storage rack that contains thousands of such pods all arranged on floor-to-ceiling shelves, each identified by row and column location. The MES maps out where Lot X500 is and where it needs to go next—the stepper station. The MES then announces Lot X500’s virtual location on the software grid.

The Fab-Wide Scheduling module, which is constantly scanning the grid for updates on the thousands of pods being processed all over the fab, sees that Lot X500 is ready for photolithography and needs to be assigned to one of the many steppers on the manufacturing floor. The scheduler also recognizes that Lot X500 is destined to become Core 2 Quad microprocessors—Intel’s four-core microprocessors, which will be fabricated at 45 nm—and determines which stepper is available and qualified to do the job.

Just as the scheduling system is constantly scanning the grid to determine tool availability and wafer locations, the tools themselves are perpetually posting information about their readiness to the software grid. In this case, Stepper No. 8 signals its tool controller that it is idle and therefore ready to accept a new lot of silicon wafers. The controller, a program that is the tool’s interface to the grid, translates the tool’s message—“I’m idle”—from a form of machine language into XML and posts it to the grid. The scheduler sees this announcement and assigns Lot X500 to Stepper No. 8, a match it subsequently posts to the grid. Now it’s time for the virtual to become real.

The Material Handling and Tool Control sees the match of lot and stepper on the grid and assigns a robot to retrieve Lot X500 from its storage unit. That assigned robot places the pod on a carrier that zooms along an overhead monorail track at 5 meters per second to the stepper station. When Lot X500 arrives at Stepper No. 8’s port, the stepper’s controller puts a request on the grid asking for processing information for this specific lot. The Advanced Process Control module sees this request, calculates the optimal recipe settings to use, and provides the settings to the stepper’s controller.

The controller also takes readings from sensors monitoring the stepper’s health and posts that data on the grid. If Stepper No. 8 runs into trouble—say, an issue with the timing of an exposure—the Statistical Process Control software module crunches the data stream coming off the tool, identifies the problem, and publishes an alarm message on the grid. This alerts the Equipment Manager module to turn the machine off.

The Exception Notification system sees that Stepper No. 8 has gone down and pages maintenance personnel—actual human beings!—to come and investigate. Engineers are dispatched to inspect the lot and the machine. Once the machine is fixed, Stepper No. 8’s status is changed from “down” to “production ready.” Depending on the scheduler’s priorities, Lot X500 is moved back to storage or on to the next step.

After Lot X500 makes it through all the processing steps, the final chips are tested and the resulting data crunched by several analysis engines in the Engineering Analysis Framework suite. These analysis programs include ones that analyze the yield of working chips out of the total produced, and they also record such transistor-performance parameters as speed and power consumption. The programs correlate the yields and performance parameters to the recipes used on Lot X500 to identify desirable tweaks to the standard Core 2 recipe.

For instance, from the level of current it takes to turn a chip’s transistors on and off, we can decide whether the kind or amount of ions that we are implanting in the silicon at an early stage needs to be changed. Within a matter of minutes, the Advanced Process Control module can send the revised recipe to the implant tool so that all wafers entering that stage can take advantage of the optimal dosage of, say, arsenic ions.

Once the entire process has been proven to work in a technology development line creating experimental chips, it is exactly copied at the production fabs. That means we make our high-volume manufacturing lines look as much like the technology development line as physically possible so we can produce millions of chips with consistent quality. We use the same pipes to deliver the same chemicals and gases to the same tools, which are laid out in the same configuration. The AMT system ensures that the same recipes are used, and it compares data across all the sites to ensure that every tool in every fab runs exactly the same way.

After a fab successfully implements the new chip-making processes, engineers start investigating ways to improve transistor performance and the yield of working chips from each wafer. As soon as they can demonstrate an improvement, it is replicated at all other sites that make the same chips. Intel typically has three high-volume manufacturing fabs making our newest chips.

Linked by a wide-area network, these three fabs work together as one virtual factory, sharing the latest manufacturing process improvements and incorporating them in exactly the same fashion. Intel’s method of precisely copying processes across all our fabs has been occasionally derided by our competition to mean that we lack flexibility and agility. On the contrary, we believe it is an effective tool to manage changes continuously while reducing risk.

This ability to constantly tweak and replicate manufacturing procedures and recipes will become even more important as we push our chips down to smaller dimensions. The software will have to evolve, too. It will take advantage of a certain silicon symbiosis—the chips made by our software in turn run that software more efficiently. This is especially important considering that each new generation of chip creates hundreds more terabytes of engineering data that our Itanium- and Xeon-based servers will have to crunch.

We’ll need all the speed we can get. Smaller dimensions in next-generation nodes means more layers of wires and more daunting process challenges in making transistors, among other things. Despite the increasing difficulty, the time allowed for development—two years—won’t change. To hit the market ahead of our competition, we will have to run a highly adaptive technology development line, where we can do things like process different kinds of chips on individual wafers to get more data from fewer wafers faster.

Intel’s AMT provides a software framework that allows us to quickly add new functions and change existing modules. We don’t want to rewrite the whole system to accommodate each new generation of microprocessor. But we can add new code to existing applications as well as add or replace whole applications, depending on the circumstances. If we want to change the manufacturing flow to add steps or to change how wafers are routed through the line, we can implement those changes in our software quickly without having to recompile the code or test the entire system. Such flexibility is key to Intel’s ability to adapt to rapid changes in fabs within and between successive generations of chips.

Software has automated all routine tasks needed to run a fab. We don’t need people to stand in front of the tools to run the wafers or make the thousands of decisions that are required every day. That said, we will always need humans to enter our fabs to conduct routine maintenance on machines and to fix them when they break down. And, of course, we need humans—including the hundreds of Ph.D.s we have working on technology development—to create the procedures and chip recipes that will help us to continue to double the number of transistors per chip every couple of years. Software has freed our engineers to investigate ways to work with silicon through the 22-nm generation of chips. And we are looking forward to the day in the not-too-distant future when our software tests recipes for chips that might use carbon nanotubes as transistors and light-emitting semiconductors for optical interconnects.

About the Authors

CHANDRA MOULI, director of fab automation software architecture, and WAYNE CARRIKER, a principal automation engineer, both work in Intel’s Logic Technology Development group in Hillsboro, Ore.

To Probe Further

The latest edition of the International Technology Roadmap for Semiconductors is available at https://www.itrs.net/reports.html.

For a general perspective on fab automation, check out the proceedings of The 17th Annual SEMI/IEEE Advanced Semiconductor Manufacturing Conference, 2006.